е…ідәҺARM Cortex

ARM Cortexзі»еҲ—еҲҶдёәдёүзұ»пјҡCortex-AпјҢCortex-RпјҢCortex-MгҖӮ

е…¶дёӯпјҢеҹәдәҺCortex-Aзҡ„еӨ„зҗҶеҷЁйҖӮеҗҲиҝҗиЎҢеҜ№жҖ§иғҪжңүжһҒй«ҳиҰҒжұӮзҡ„зі»з»ҹпјҢеҰӮжһңжҳҜжңүжҜ”иҫғй«ҳжҖ§иғҪзҡ„еҗҢж—¶пјҢиҝҳйңҖиҰҒдҝқиҜҒе®һж—¶жҖ§пјҢеҲҷйҖӮеҗҲйҮҮз”ЁCortex-Rжһ¶жһ„зҡ„еӨ„зҗҶиҠҜзүҮпјҢCortex-MеҲҷйҖӮеҗҲе…¶д»–еә”з”ЁдәҺеөҢе…ҘејҸзі»з»ҹзҡ„еҫ®жҺ§еҲ¶еҷЁиҠҜзүҮгҖӮ[1]

е…ідәҺARM Cortex-R52

дҪңдёәеҹәдәҺARMv8-Rжһ¶жһ„дёӢзҡ„第дёҖж¬ҫRж ёеӨ„зҗҶеҷЁпјҢCortex-R52жӢҘжңү4дёӘж ёеҝғпјҢйҮҮз”Ё16зәізұіе·ҘиүәпјҢжңҖй«ҳж—¶й’ҹйў‘зҺҮдёә1.6GHzгҖӮ[2]

R52жҳҜдёҖж¬ҫ32дҪҚзҡ„й«ҳжҖ§иғҪе®һж—¶еӨ„зҗҶеҷЁпјҢжӢҘжңүжһҒй«ҳзҡ„еҠҹиғҪе®үе…Ёж ҮеҮҶпјҢеҗҢж—¶д№ҹжһҒе…·зҒөжҙ»жҖ§пјҢ4дёӘж ёеҝғж—ўеҸҜд»ҘзӢ¬з«ӢиҝҗиЎҢпјҢд№ҹеҸҜд»Ҙй…ҚзҪ®дёәиҮіеӨҡ4ж ёй”ҒжӯҘжҲ–иҖ…split-lockгҖӮR52жӢҘжңүдёӨзә§MPUпјҢеҗ„иҮӘеҸҜи®ҫзҪ®24еҲҶеҢәпјҢеҲҶеҢәжңҖе°ҸеҸҜд»Ҙдёә64еӯ—иҠӮгҖӮ

Cortex-R52ж”ҜжҢҒ硬件ејәеҲ¶пјҲhardware-enforcedпјүиҪҜ件еҲҶзҰ»еҠҹиғҪпјҢд»ҘзЎ®дҝқйңҖиҰҒз»қеҜ№е®үе…Ёзҡ„д»Јз Ғиў«е®Ңе…Ёйҡ”зҰ»гҖӮиҝҷдҪҝеҫ—硬件еҸҜз”ұиҪҜ件管зҗҶзЁӢеәҸз®ЎзҗҶпјҢзӣ‘зқЈд»»еҠЎзҡ„жү§иЎҢе’Ңиө„жәҗеҲҶй…ҚгҖӮйҖҡиҝҮзІҫеҮҶдё”е®Ңе–„зҡ„иҪҜ件еҲҶзҰ»пјҢCortex-R52еҮҸе°‘дәҶеҝ…йЎ»йҖҡиҝҮе®үе…Ёи®ӨиҜҒзҡ„д»Јз ҒйҮҸпјҢз®ҖеҢ–дәҶиҪҜ件йӣҶжҲҗгҖҒз»ҙжҠӨе’ҢйӘҢиҜҒпјҢд»ҺиҖҢеҠ еҝ«дәҶз ”еҸ‘иҝӣзЁӢгҖӮ[3]

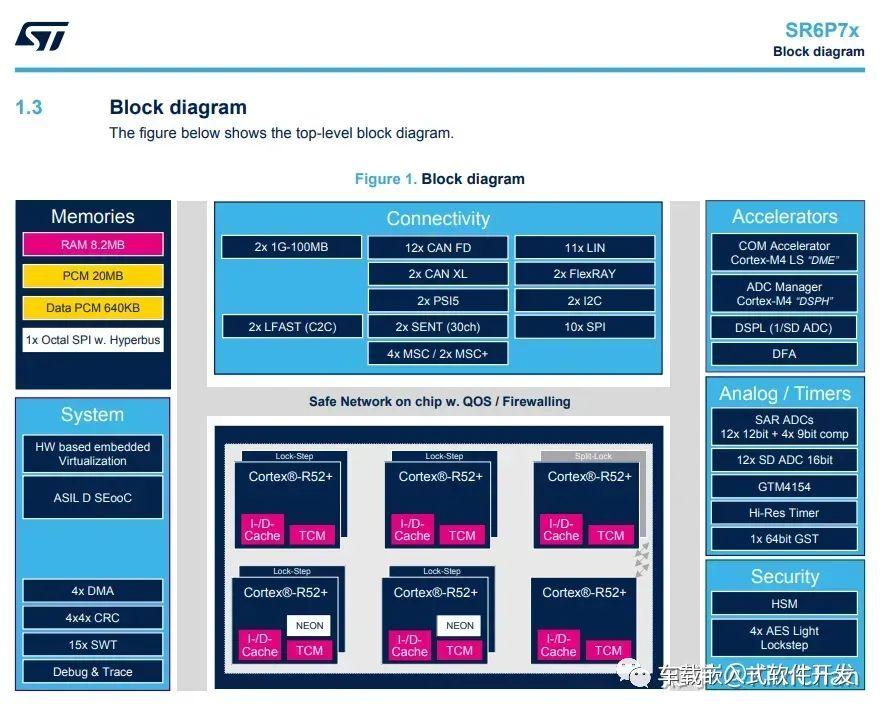

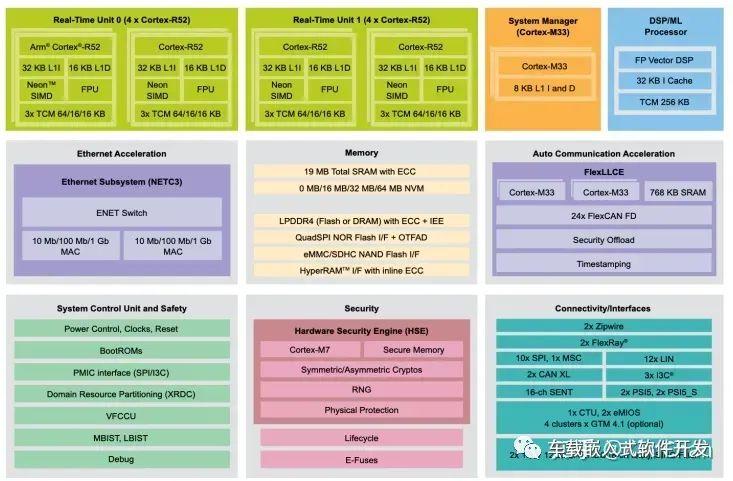

NXP S32ZдёҺST SR6P7G7

иҝ‘жңҹе…іжіЁеҲ°зҡ„S32ZпјҢе°ұжҳҜйҮҮз”ЁдәҶCortex-R52жһ¶жһ„пјҢеҸҰеӨ–пјҢSR6P7G7еҲҷйҮҮз”Ёзҡ„жҳҜCortex-R52зҡ„еҚҮзә§зүҲCortex-R52+гҖӮпјҲе…ідәҺR52/R52+зҡ„еҢәеҲ«пјҢиҜ·еҸӮиҖғй“ҫжҺҘ[4]пјү

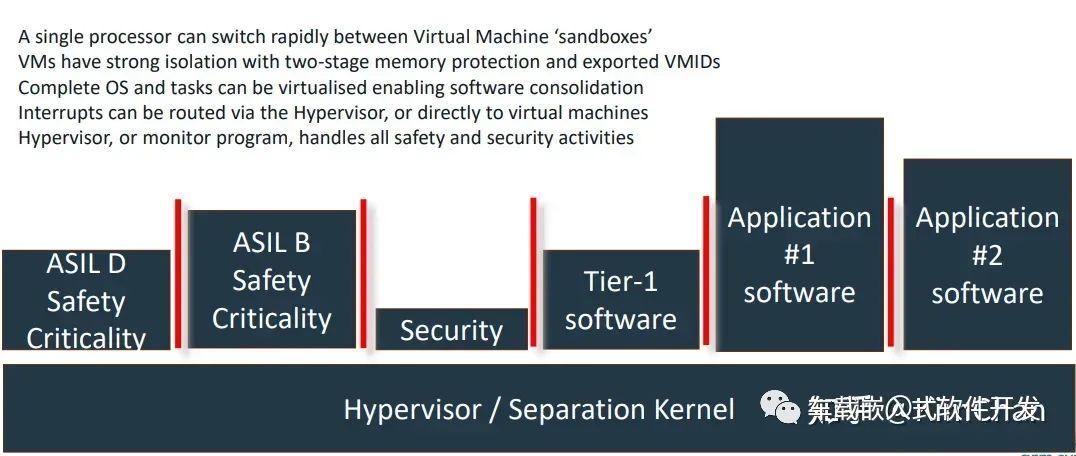

жң¬ж–ҮдёҚеҜ№иҝҷдёӨж¬ҫиҠҜзүҮеҒҡе…·дҪ“и§ЈиҜ»пјҢдҪҶйҖүз”ЁиҝҷдёӨж¬ҫиҠҜзүҮзҡ„еңәжҷҜдёӢпјҢеә”иҜҘдёҚдјҡй”ҷиҝҮеҹәдәҺARMv8-Rзҡ„ж–°зү№жҖ§пјҢд№ҹеҚіжң¬ж–Үе°Ҷдё»иҰҒд»Ӣз»Қзҡ„иҷҡжӢҹеҢ–зү№жҖ§пјҢиғҪеӨҹеё®еҠ©ејҖеҸ‘иҖ…жңүж•ҲеҗҲзҗҶең°е°ҶеӨҡдёӘдј з»ҹеҲҶеёғејҸECUзҡ„еҠҹиғҪйӣҶжҲҗеңЁдёҖдёӘжҺ§еҲ¶еҷЁдёӯ[5]гҖӮдҫӢеҰӮпјҢеҹәдәҺиҝҷдёӘзү№жҖ§пјҢејҖеҸ‘иҖ…еҸҜд»Ҙе°ҶдёҚеҗҢзҡ„еҠҹиғҪе®үе…Ёзӯүзә§иҰҒжұӮпјҢдҝЎжҒҜе®үе…Ёзӯүзә§иҰҒжұӮпјҢйңҖиҰҒOTAеҚҮзә§зҡ„иҪҜ件пјҢеҲ’еҲҶеҲ°дёҚеҗҢзҡ„иҷҡжӢҹжңәдёӯеҒҡејәйҡ”зҰ»гҖӮ

дёӨз§ҚиҷҡжӢҹжңәпјҹ

з”ұдәҺдёҚеҗҢзҡ„жқҘжәҗеҜ№дәҺеөҢе…ҘејҸиҷҡжӢҹжңәзҡ„иҜҙжі•жңүдёҖдәӣзЁҚи®ёеҢәеҲ«пјҢдҪҶд»ҺжҠҖжңҜдёҠпјҢдё»иҰҒеҲҶдёәдёӨз§ҚпјҡHypervisorд»ҘеҸҠSeparation KernelгҖӮ

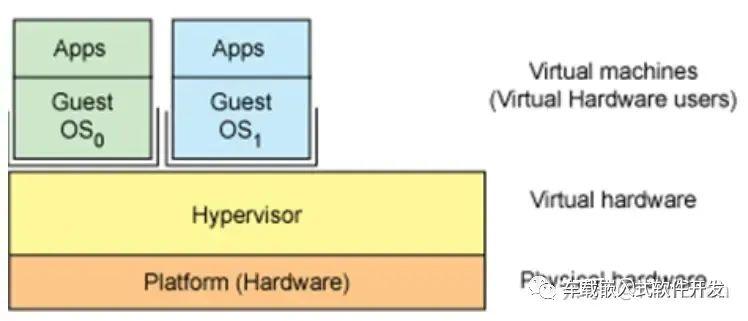

Hypervisor

HypervisorпјҢд№ҹиў«з§°дёәиҷҡжӢҹжңәзӣ‘и§ҶеҷЁпјҲvirtual machine monitor, VMMпјүпјҢдҪңдёәз”өи„‘иҪҜ件пјҢеӣә件жҲ–иҖ…硬件пјҢеҸҜд»ҘеҲӣе»ә并иҝҗиЎҢиҷҡжӢҹжңәгҖӮиў«hypervisorз”ЁжқҘжү§иЎҢдёҖдёӘжҲ–еӨҡдёӘиҷҡжӢҹжңәзҡ„з”өи„‘з§°дёәе®ҝдё»жңәпјҲhost machineпјүпјҢиҝҷдәӣиҷҡжӢҹжңәеҲҷз§°дёәе®ўжҲ·жңәпјҲguest machineпјүгҖӮHypervisor жҸҗдҫӣиҷҡжӢҹзҡ„дҪңдёҡе№іеҸ°жқҘжү§иЎҢе®ўжҲ·ж“ҚдҪңзі»з»ҹпјҲguest operating systemsпјүпјҢиҙҹиҙЈз®ЎзҗҶе…¶д»–е®ўж“ҚдҪңзі»з»ҹзҡ„жү§иЎҢйҳ¶ж®өпјӣиҝҷдәӣе®ўжҲ·ж“ҚдҪңзі»з»ҹпјҢе…ұеҗҢеҲҶдә«иҷҡжӢҹеҢ–еҗҺзҡ„硬件иө„жәҗгҖӮ[6]з”ұдәҺHypervisorеҲҶзҰ»дәҶеҗ„иҷҡжӢҹжңәпјҢеҗ„иҷҡжӢҹжңәеҶ…йғЁзҡ„еҠЁдҪң并дёҚдјҡеҪұе“Қе…¶д»–иҷҡжӢҹжңәгҖӮ

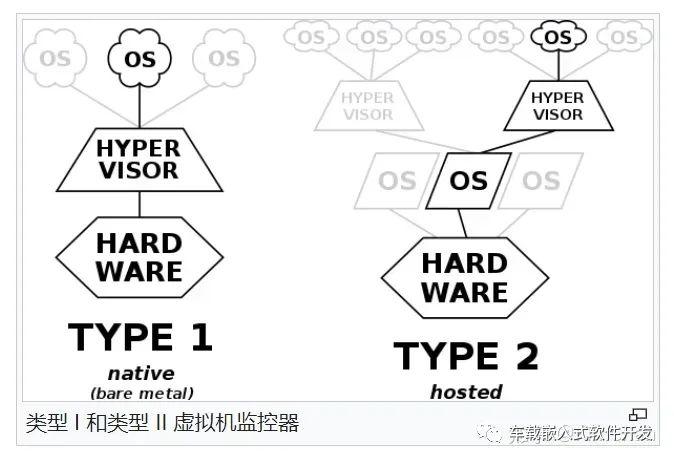

д»ҺVMдҪҝз”Ёиө„жәҗзҡ„и§’еәҰпјҢеҸҜд»Ҙе°ҶHypervisorеҲҶжҲҗдёӨзұ»пјҡType-1дёҺType-2гҖӮType-1зҡ„HypervisorзӣҙжҺҘиҝҗиЎҢеңЁзү©зҗҶ硬件дёҠ(жңүж—¶д№ҹз§°д№ӢдёәиЈёжңәиҷҡжӢҹеҷЁжҲ–иҖ…жң¬ең°иҷҡжӢҹжңә)пјҢType-2зҡ„HypervisorзӣҙжҺҘиҝҗиЎҢеңЁдёҖдёӘж“ҚдҪңзі»з»ҹ(иҜҘж“ҚдҪңзі»з»ҹиҝҗиЎҢеңЁзү©зҗҶ硬件)дёҠйқўгҖӮ[7]

Type-1 HypervisorйңҖиҰҒ硬件ж”ҜжҢҒпјҢиҝҗиЎҢж•ҲзҺҮй«ҳпјҢType-2 Hypervisorе°ұеғҸе…¶д»–и®Ўз®—жңәзЁӢеәҸдёҖж ·иҝҗиЎҢеңЁж“ҚдҪңзі»з»ҹдёҠпјҢиҝҗиЎҢж•ҲзҺҮиҫғType-1жҜ”иҰҒдҪҺгҖӮ[6]

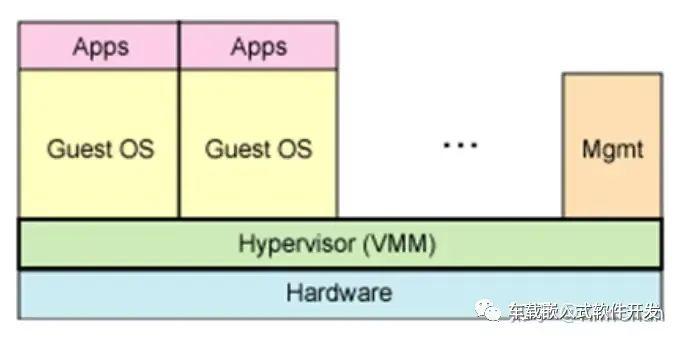

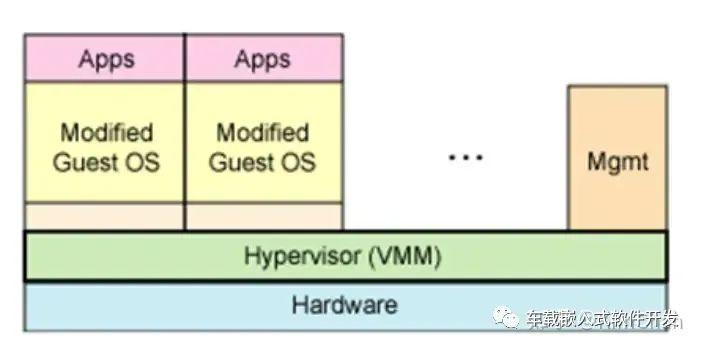

HypervisorжҸҗдҫӣ硬件иө„жәҗзҡ„иҷҡжӢҹеҢ–пјҢж №жҚ®жҠҖжңҜзҡ„дёҚеҗҢпјҢеҸҜд»ҘеҲҶжҲҗе®Ңе…ЁиҷҡжӢҹеҢ–жҠҖжңҜ(Full Virtualization)е’ҢеҚҠиҷҡжӢҹеҢ–жҠҖжңҜ(Paravirtualization)пјҢеҢәеҲ«е°ұжҳҜеҚҠиҷҡжӢҹеҢ–йңҖиҰҒдҝ®ж”№Guest OSпјҢиғҪеӨҹе°ҶдёҖйғЁеҲҶAPIж“ҚдҪңж— йңҖеҖҹеҠ©HypervisorиҝӣиЎҢзҝ»иҜ‘пјҢзӣҙжҺҘдёҺ硬件дәӨдә’гҖӮ

Separation Kernel

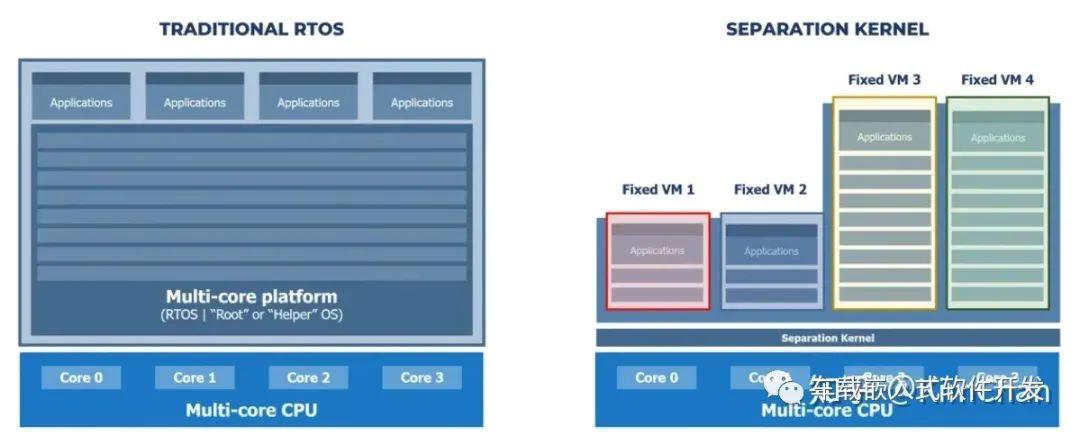

ж— и®әжҳҜдҪҝз”ЁдҪ•з§Қзұ»еһӢзҡ„HypervisorпјҢдёәдәҶжҸҗдҫӣиҷҡжӢҹеҢ–жҠҖжңҜпјҢйғҪйңҖиҰҒж¶ҲиҖ—дёҖе®ҡзҡ„зі»з»ҹиө„жәҗгҖӮдёәдәҶеңЁеөҢе…ҘејҸйўҶеҹҹд№ҹиғҪеј•е…ҘиҷҡжӢҹжңәзҡ„жҰӮеҝөпјҲеөҢе…ҘејҸйўҶеҹҹд№ҹиғҪз§°д№ӢдёәеҲҶеҢәпјҢpartitionпјүпјҢдёҖз§Қзү№еҲ«зұ»еһӢзҡ„Hypervisorе°ұжҳҜSeparation KernelпјҲйҡ”зҰ»еҶ…ж ёпјүгҖӮ

йҡ”зҰ»еҶ…ж ёд»…д»…еҒҡйҡ”зҰ»пјҢжІЎжңүи®ҫеӨҮй©ұеҠЁ/з”ЁжҲ·жЁЎеһӢ/shellи®ҝй—®/еҠЁжҖҒеҶ…еӯҳпјҢеҰӮжңүйңҖиҰҒпјҢиҝҷдәӣйғҪжҳҜеңЁиҷҡжӢҹжңәйҮҢзҡ„е®ўжҲ·зЁӢеәҸдёӯе®һзҺ°зҡ„гҖӮеҰӮжӯӨпјҢйҡ”зҰ»еҶ…ж ёеҸҜд»Ҙе®һзҺ°зҡ„йқһеёёзІҫз®ҖпјҢе®ҡд№үеҘҪеӣәе®ҡзҡ„иҷҡжӢҹжңәпјҲд»ҘеҸҠеҲҶй…Қиө„жәҗпјүпјҢжҺ§еҲ¶ж¶ҲжҒҜдәӨдә’жөҒе°ұеҸҜд»ҘдәҶгҖӮ[8]

йҡ”зҰ»еҶ…ж ёзҡ„д»Јз ҒйҮҸзІҫз®Җзҡ„дјҳеҠҝеҚіжҳҜпјҢжӣҙе®№жҳ“е®һзҺ°е№¶йӘҢиҜҒе®ғжҳҜе®үе…Ёзҡ„пјҢиҝҷеңЁеҪ“еүҚйңҖиҰҒдҝқиҜҒй«ҳзӯүзә§еҠҹиғҪе®үе…Ёзҡ„иҪҰиҪҪзі»з»ҹдёӯе°ӨдёәйҮҚиҰҒгҖӮз”ұдәҺж— йңҖжҸҗдҫӣиҷҡжӢҹеҢ–пјҢиҷҡжӢҹжңәеҜ№дәҺ硬件зҡ„ж“ҚдҪңж— йңҖеҶ…ж ёзҝ»иҜ‘пјҢеҰӮжһңжІЎжңүиҷҡжӢҹжңәй—ҙзҡ„ж¶ҲжҒҜиҜ·жұӮпјҢйҡ”зҰ»еҶ…ж ёеңЁиҝҗиЎҢж—¶з”ҡиҮіеҸҜд»Ҙи®ӨдёәжҳҜвҖңдёҚеӯҳеңЁзҡ„вҖқпјҢеҗ„иҷҡжӢҹжңәеҸҜд»ҘжӢҘжңүдёҺд№ӢеүҚжІЎжңүе·®ејӮзҡ„е®һж—¶иЎЁзҺ°гҖӮ

Why Cortex-R52пјҹ

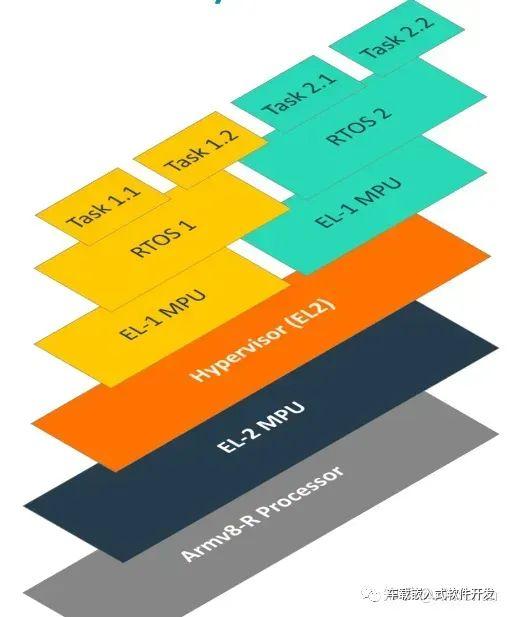

ж №жҚ®еүҚж–ҮжүҖиҜҙпјҢдёәдәҶеңЁдёҖдёӘMCUдёҠиҝҗиЎҢжүҖи°“зҡ„еӨҡдёӘзЁӢеәҸпјҢйңҖиҰҒжңүHypervisorпјҢGuest OSпјҲin VMпјүд»ҘеҸҠдёҠеұӮеә”з”ЁгҖӮдёәдәҶеҜ№зЎ¬д»¶иө„жәҗжңүдёҚеҗҢзҡ„жҺ§еҲ¶жқғйҷҗпјҢCortex-R52пјҲеҹәдәҺARMv8пјүжҸҗдҫӣдёүзә§Exception levelпјҢд№ҹеҚіEL0-EL2гҖӮ

Exception Level

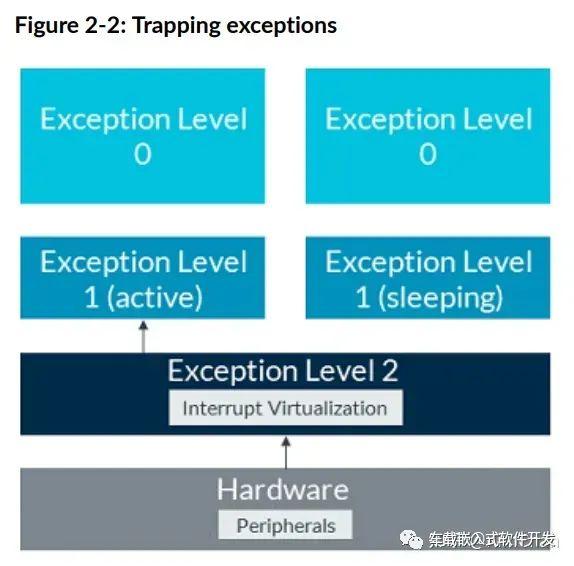

EL0жӢҘжңүжңҖдҪҺзҡ„иҪҜ件жү§иЎҢжқғйҷҗпјҢд№ҹиў«з§°дҪңдёәйқһзү№жқғжү§иЎҢпјҢEL1дёҺEL2жӢҘжңүжӣҙй«ҳзҡ„иҪҜ件жү§иЎҢзү№жқғпјҢиҖҢеңЁEL2зә§еҲ«пјҢеҲҷжҸҗдҫӣеӨ„зҗҶеҷЁиҷҡжӢҹеҢ–зү№жҖ§гҖӮи§ҰеҸ‘дёҖдёӘexceptionпјҢжҲ–жҳҜд»ҺжҹҗдёҖдёӘexceptionиҝ”еӣһпјҢиҪҜ件жү§иЎҢеҸҜд»ҘеңЁдёҚеҗҢзҡ„ELй—ҙиҪ¬з§»пјҢи§ҰеҸ‘exceptionеҸӘиғҪи§ҰеҸ‘еҪ“еүҚзә§еҲ«жҲ–иҖ…жӣҙй«ҳзӯүзә§зҡ„exceptionпјҢж— жі•йҷҚзә§пјҢеҰӮжһңжҳҜд»ҺжҹҗдёҖELиҝ”еӣһпјҢеҸӘиғҪдҝқжҢҒеңЁеҪ“еүҚELзә§еҲ«жҲ–иҖ…йҷҚеҲ°жӣҙдҪҺзӯүзә§зҡ„ELгҖӮеҸҰеӨ–пјҢж— жі•и§ҰеҸ‘дёҖдёӘзӣ®ж ҮELзӯүзә§дёәEL0зҡ„exceptionгҖӮ[9]

иҝҷж ·пјҢдёҖиҲ¬ең°пјҢHypervisorиҝҗиЎҢеңЁжҸҗдҫӣеӨ„зҗҶеҷЁиҷҡжӢҹеҢ–зҡ„EL2зә§еҲ«пјҢGuest OSиҝҗиЎҢеңЁEL1зә§еҲ«пјҢиҖҢеҗ„дёӘдёҠеұӮеә”з”ЁзЁӢеәҸеҲҷиҝҗиЎҢеңЁEL0зә§еҲ«гҖӮ

дёӨзә§еҶ…еӯҳдҝқжҠӨ

йҷӨжӯӨд№ӢеӨ–пјҢR52пјҲжҲ–иҖ…иҜҙARMv8-Rж ёеҝғпјүж”ҜжҢҒдёӨзә§MPUпјҢEL-1 MPUе’Ңд№ӢеүҚеңЁе…¶д»–иҠҜзүҮдёҠдҪҝз”Ёзҡ„MPUеҠҹиғҪдёҖж ·пјҢдҪҶжҳҜR52ж–°еўһзҡ„EL-2 MPUж—ўеҸҜд»ҘжҸҗдҫӣEL2зә§еҲ«еҜ№дәҺеӯҳеӮЁзҡ„и®ҝй—®дҝқжҠӨпјҲstage 1пјүпјҢд№ҹиғҪжҸҗдҫӣд»ҺEL1/EL0зә§еҲ«зҡ„еӯҳеӮЁи®ҝй—®иҜ·жұӮзҡ„дҝқжҠӨпјҲstage 2пјүгҖӮR52ж”ҜжҢҒдёӨзә§дҝқжҠӨзҡ„ең°еқҖиҪ¬жҚўгҖӮ

дёӯж–ӯиҷҡжӢҹеҢ–

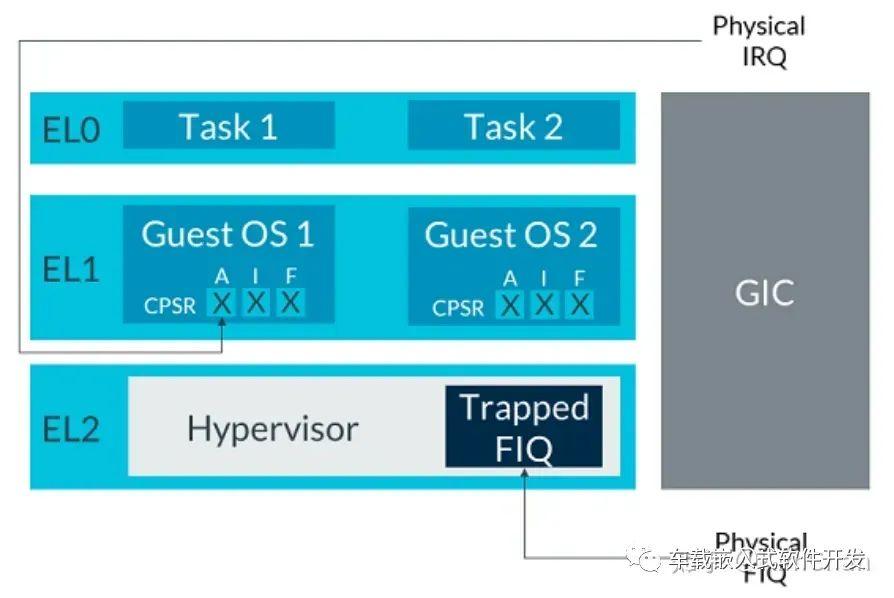

HCRпјҲHyp Configuration Registerпјүе’ҢGICпјҲGeneric Interrupt ControllerпјүпјҢйғҪдјҡдҪҝз”ЁеҲ°иҷҡжӢҹдёӯж–ӯгҖӮ

HypervisorдҪҝз”ЁиҷҡжӢҹдёӯж–ӯе°Ҷдёӯж–ӯеҲҶеҸ‘еҲ°еҜ№еә”зҡ„guest OSпјҢеҜ№дәҺguest OSжқҘиҜҙпјҢеӨ„зҗҶдёӯж–ӯе’ҢеӨ„зҗҶзү©зҗҶдёӯж–ӯжІЎжңүеҢәеҲ«гҖӮ

иҷҡжӢҹдёӯж–ӯеҸӘиғҪз”ұEL2зә§еҲ«еҲӣе»әгҖӮ

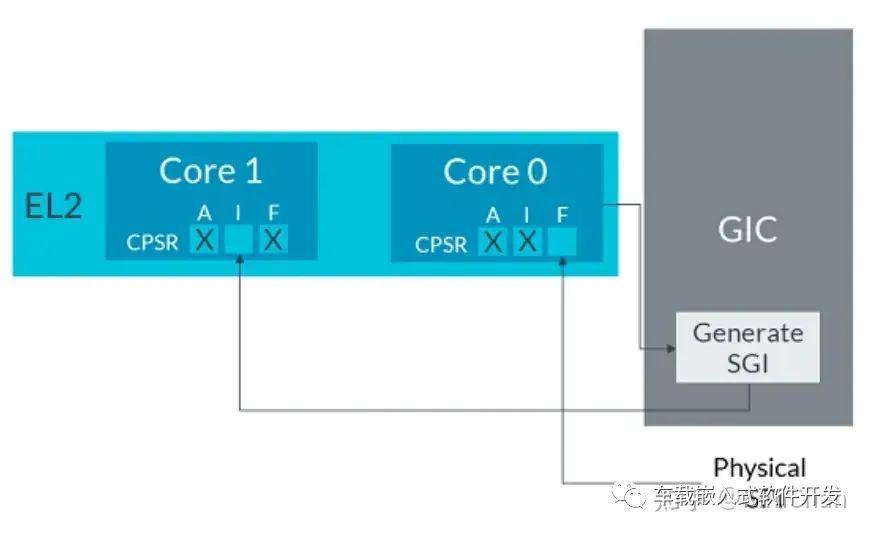

еҰӮжһңи®ҫзҪ®дәҶHCRпјҢз”ұhypervisorжҚ•иҺ·exceptionпјҢеҪ“exceptionиў«жҚ•иҺ·дәҺEL1/EL0пјҢCPSRеҜ„еӯҳеҷЁзҡ„F(FIQ mask bit)/I(IRQ mask bit)/A(Asynchronous (imprecise) abort disable bit)ж Үеҝ—дҪҚдјҡиў«еҝҪз•ҘпјҢзЁӢеәҸдјҡз«ӢеҚіи·іиҪ¬еҲ°еҜ№еә”EL2зҡ„exception handlerгҖӮ

еҪ“жҹҗдёҖexceptionй…ҚзҪ®дёәEL2жҚ•иҺ·пјҢдё”еҸ‘з”ҹеңЁEL2/EL1/EL0зЁӢеәҸжү§иЎҢж—¶пјҢж Үеҝ—дҪҚF/I/Aдјҡиө·дҪңз”ЁгҖӮF/I/AдҪңдёәжҺ©з ҒжқҘзЎ®е®ҡEL1/EL0зҡ„иҷҡжӢҹдёӯж–ӯжҲ–иҖ…EL2зҡ„зү©зҗҶдёӯж–ӯжҳҜеҗҰдјҡиў«еҪ“еҒҡexceptionеӨ„зҗҶгҖӮ

еҰӮжһңжІЎжңүи®ҫзҪ®HCRеҺ»жҚ•иҺ·exceptionпјҢйӮЈд№ҲEL1еҸ‘з”ҹзҡ„exceptionд»Қж—§з”ұEL1еӨ„зҗҶгҖӮ

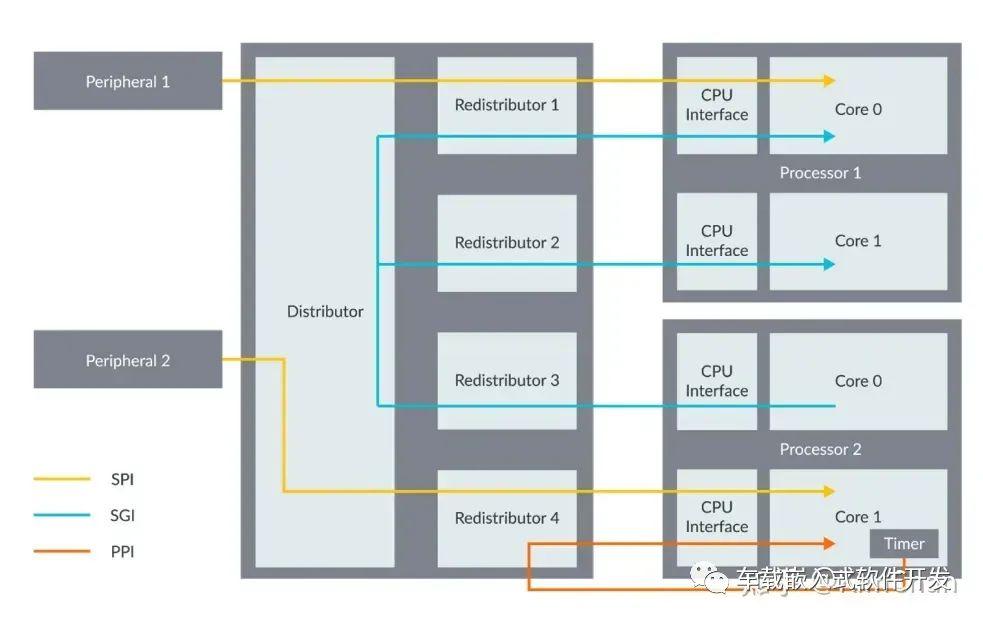

еҜ№дәҺGICпјҢе®ғдјҡеҜ№дёӯж–ӯиҝӣиЎҢеҲҶеҸ‘пјҢдҫӢеҰӮе°ҶеӨ–и®ҫдә§з”ҹзҡ„SPIпјҲshared peripheral interruptsпјҢе…ұдә«еӨ–и®ҫдёӯж–ӯпјүпјҢиҪ¬еҸ‘еҲ°дёҖдёӘе…·дҪ“ж ёеҝғдёҠпјҢжҲ–жҳҜе°ҶжҹҗдёҖж ёеҝғи§ҰеҸ‘зҡ„SGIпјҲsoftware generated interruptsпјҢиҪҜ件з”ҹжҲҗдёӯж–ӯпјүеҲҶеҸ‘еҲ°еҸҰеӨ–дёҖдёӘж ёеҝғпјҢдҪңж ёй—ҙйҖҡдҝЎз”ЁгҖӮ

йҷӨжӯӨд№ӢеӨ–пјҢиҝҳжңүPPIпјҲprivate peripheral interruptsпјҢз§ҒжңүеӨ–и®ҫдёӯж–ӯпјүпјҢеҸӘиғҪеңЁжҹҗдёҖдёӘж ёеҝғдёӯеӯҳеңЁпјҢж— жі•иў«е…¶д»–ж ёеҝғжҺҘ收еҲ°гҖӮ

з”ұдәҺиҷҡжӢҹдёӯж–ӯзҡ„еӯҳеңЁпјҢGICеҸҜд»Ҙе°ҶжҹҗдёҖзү©зҗҶдёӯж–ӯе…іиҒ”еҲ°жҹҗдёҖиҷҡжӢҹдёӯж–ӯпјҢ并иҝӣиЎҢеҲҶеҸ‘еҲ°жҹҗдёҖдёӘж ёеҝғдёҠгҖӮиҷҡжӢҹдёӯж–ӯеҸҜд»ҘзӢ¬з«ӢеӯҳеңЁпјҢдёҚйңҖиҰҒдёҖе®ҡеҜ№еә”еҲ°зү©зҗҶдёӯж–ӯгҖӮ

иҷҡжӢҹе®ҡж—¶еҷЁ

дёҚеҗҢзҡ„guest OSжӢҘжңүеҗ„иҮӘзҡ„иҷҡжӢҹе®ҡж—¶еҷЁпјҢдё”д»…еңЁеҗ„иҮӘguest OSжҙ»еҠЁзҠ¶жҖҒдёӢжүҚи®°еҪ•ж—¶й—ҙгҖӮдҫӢеҰӮжҹҗдёҖ10з§’ж—¶й—ҙеҶ…пјҢжңүдёӨдёӘguest OSеҲҶеҲ«жү§иЎҢдәҶ5з§’пјҢйӮЈд№Ҳеҗ„иҮӘзҡ„е®ҡж—¶еҷЁд№ҹеҸӘдјҡи®°еҪ•5з§’зҡ„ж—¶й—ҙгҖӮ

иҷҡжӢҹжңәID

дёәдәҶеҢәеҲҶиҷҡжӢҹжңәзҡ„дёҚеҗҢпјҢHypervisorдјҡдёәдёҚеҗҢзҡ„иҷҡжӢҹжңәеҲҶй…ҚдёҚеҗҢзҡ„IDпјҢеҪ“guest OSи®ҝй—®еӨ–и®ҫж—¶пјҢжҖ»зәҝдёҠдјҡжңүIDдҝЎжҒҜпјҢиҝҷж ·е°ұеҸҜд»Ҙж №жҚ®и®ҝй—®йҷҗеҲ¶иҝӣиЎҢиҜ·жұӮиҝҮж»ӨдәҶгҖӮеҜ№дәҺжҜҸдёӘи®ҫеӨҮжҲ–еҜ„еӯҳеҷЁпјҢйғҪз”ұSMPUпјҲSystem Memory Protection UnitпјүиҝӣиЎҢдҝқжҠӨгҖӮ

еҜ„еӯҳеҷЁеӨҮд»Ҫ

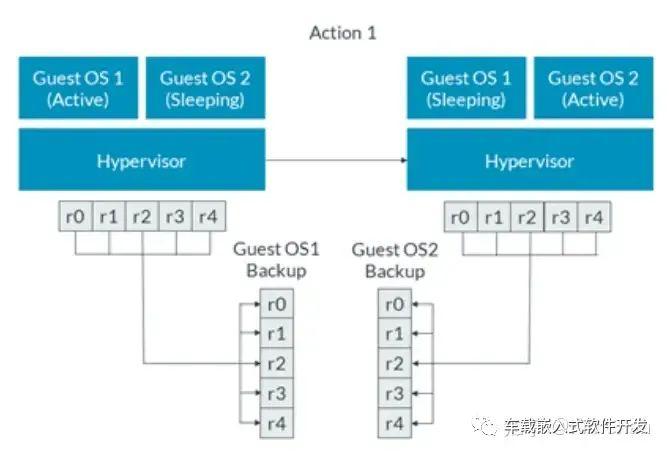

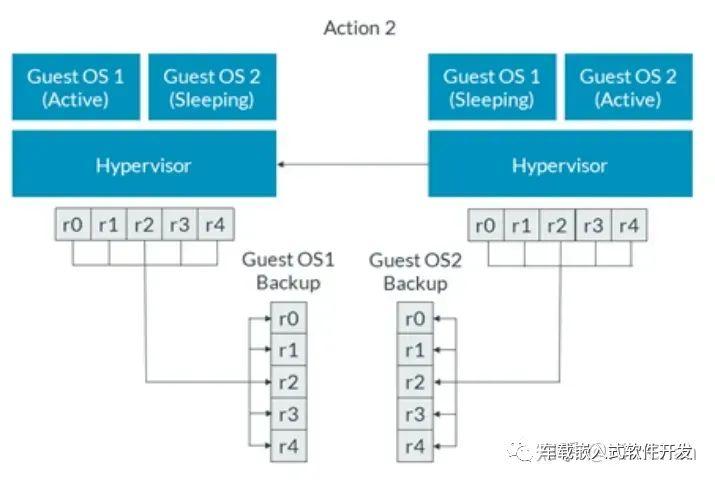

еҲӣе»әиҷҡжӢҹжңәзҡ„дёҖдёӘйҮҚиҰҒйғЁеҲҶжҳҜпјҢguest OSиғҪеӨҹиў«жҡӮеҒңжү§иЎҢпјҢд№ӢеҗҺеҶҚжҒўеӨҚгҖӮеҪ“жҡӮеҒңжү§иЎҢж—¶пјҢиҷҡжӢҹжңәзҡ„зҠ¶жҖҒеҝ…йЎ»иў«дҝқеӯҳдёӢжқҘпјҢз”ұhypervisorдҪңеӨҮд»ҪгҖӮеҰӮжһңйңҖиҰҒеҶҚж¬ЎжҝҖжҙ»guest OSзҡ„жү§иЎҢпјҢhypervisorдјҡд»ҺеӨҮд»ҪдёӯжҒўеӨҚеҜ„еӯҳеҷЁдҝЎжҒҜгҖӮеҰӮдёӢж–№дёӨеј еӣҫжүҖзӨәпјҢAction1/2дәӨжӣҝжү§иЎҢгҖӮ

EB/Vector/ETASзҡ„дә§е“Ғпјҹ

е…іжіЁйўҶеҹҹжңүйҷҗпјҢжӯӨеӨ„д»…и®°еҪ•йғЁеҲҶAUTOSARдҫӣеә”е•ҶжүҖжҸҗдҫӣзҡ„MCUз«ҜHypervisorдә§е“ҒгҖӮ

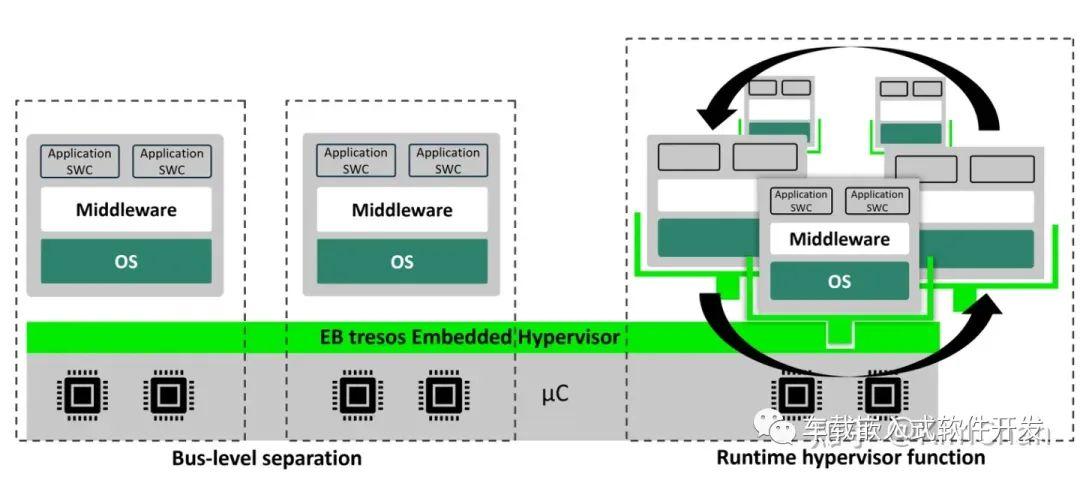

EBпјҡEB tresos Embedded Hypervisor вҖ“ Elektrobit пјҲSeparation Kernel/Hypervisorпјү

ETASпјҡRTA-LWHVR - RTA Software Products - ETASпјҲSeparation Kernel/Hypervisorпјү

VectorпјҡSafe and Efficient Virtualization With MICROSAR Classic veHypervisor | VectorпјҲSeparation Kernel/Hypervisorпјү

жӢ¬еҸ·еҶ…жіЁйҮҠд»…ж №жҚ®е®ҳж–№йЎөйқўеҶ…е®№и®°еҪ•жҺЁжөӢе…¶дә§е“ҒжүҖж”ҜжҢҒиҢғеӣҙпјҢеҰӮжңүй”ҷиҜҜиҝҳиҜ·жҢҮжӯЈгҖӮ

еҸӮиҖғ

^Which ARM Cortex Core Is Right for Your Application: A, R or M? https://www.silabs.com/documents/public/white-papers/Which-ARM-Cortex-Core-Is-Right-for-Your-Application.pdf

^Cortex-R52 Technical-Specifications https://developer.arm.com/Processors/Cortex-R52#Technical-Specifications

^ARMжҺЁеҮәйқўеҗ‘ж— дәәй©ҫ驶зҡ„е®үе…ЁеӨ„зҗҶеҷЁCortex-R52 https://www.eet-china.com/news/201609210921.html

^What are the major differences between Cortex-R52 and Cortex-R52+ https://developer.arm.com/documentation/ka005377/1-0/?lang=en

^й«ҳж•Ҳзҡ„еӨҡECUйӣҶжҲҗпјҡеҹәдәҺжҒ©жҷәжөҰS32е®һж—¶еӨ„зҗҶеҷЁе’ҢиҷҡжӢҹжңәзҡ„еӨҡеә”з”ЁејҖеҸ‘ https://www.nxp.com.cn/pages/multi-application-hosting-and-virtualization-on-s32-real-time-processors-for-effective-multi-ecu-consolidation:TIP-S32ZE-TRAINING-CN

^abHypervisor https://en.wikipedia.org/wiki/Hypervisor

^еөҢе…ҘејҸиҷҡжӢҹеҢ–жҠҖжңҜ http://www.prtos.org/embedded-hypervisor/

^WHAT IS A SEPARATION KERNEL? https://www.lynx.com/embedded-systems-learning-center/what-is-a-separation-kernel

^Exception levels https://developer.arm.com/documentation/100026/0104/Programmers-Model/Armv8-R-AArch32-architecture-concepts/Exception-levels?lang=en