xRDCз®Җд»Ӣ

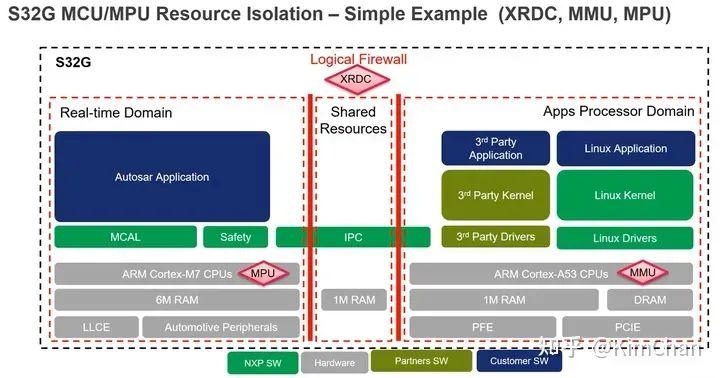

йЎ№зӣ®дёҠпјҢжңүеҫҲеӨҡеӨ–и®ҫе’ҢеҶ…еӯҳиө„жәҗйғҪеҸҜд»Ҙиў«еҲ©з”ЁпјҢдҫӢеҰӮж ёеҝғпјҢжҖ»зәҝпјҢеҶ…еӯҳеҢәеҹҹпјҢд»ҺеӨ–и®ҫзӯүзӯүгҖӮдёәдәҶиғҪеӨҹе°Ҷиҝҷдәӣиө„жәҗеҲ’еҲҶеҲ°дёҚеҗҢзҡ„еҲҶеҢәжҲ–иҖ…еҹҹдёӯпјҢжҲ‘们йңҖиҰҒеҖҹеҠ©xRDCе®ҢжҲҗпјҢз”ұxRDCжқҘз®ЎзҗҶи®ҝй—®жқғйҷҗпјҢзі»з»ҹеҶ…еӯҳдҝқжҠӨе’ҢеӨ–и®ҫйҡ”зҰ»зӯүзӯүгҖӮ

еҲ’еҲҶзҡ„еҹҹпјҢеҸҜд»ҘдёәжҜҸз§Қзү№жқғзӯүзә§е®ҡд№үи®ҝй—®жқғйҷҗзӯ–з•ҘпјҢе…ідәҺArmзҡ„зү№жқғзӯүзә§д»Ӣз»ҚпјҢеҸҜд»ҘеҸӮиҖғпјҡ

еҹәдәҺxRDCеҲҶй…ҚдёҚеҗҢзҡ„иө„жәҗпјҢеҸҜд»ҘдёәеҗҢдёҖиҠҜзүҮдёҠзҡ„еә”з”ЁејәеҲ¶еә”з”ЁFFIгҖӮеёёи§Ғзҡ„еә”з”ЁеңәжҷҜжңүпјҡ

йҡ”зҰ»е®һж—¶еә”з”Ёе’Ңйқһе®һж—¶еә”з”Ё

йҡ”зҰ»е®үе…Ёд»Јз Ғе’Ңйқһе®үе…Ёд»Јз Ғ

йҡ”зҰ»з¬¬дёүж–№йқһеҸҜдҝЎеә”з”Ёе’ҢеҸҜдҝЎеә”з”Ё

xRDCжІЎжңүиҮӘе·ұзҡ„дёӯж–ӯпјҢеҰӮжһңзӣ‘жөӢеҲ°йқһжі•и®ҝй—®пјҢеңЁMж ёдёҠдјҡеј•еҸ‘Bus FaultејӮеёёпјҢеңЁAж ёдёҠдјҡеј•еҸ‘Data AbortејӮеёёгҖӮе…ідәҺMж ёдёҠејӮеёёзҡ„е…¶д»–зұ»еһӢпјҢеҸҜд»ҘеҸӮиҖғпјҡ

xRDCеӯҗжЁЎеқ—

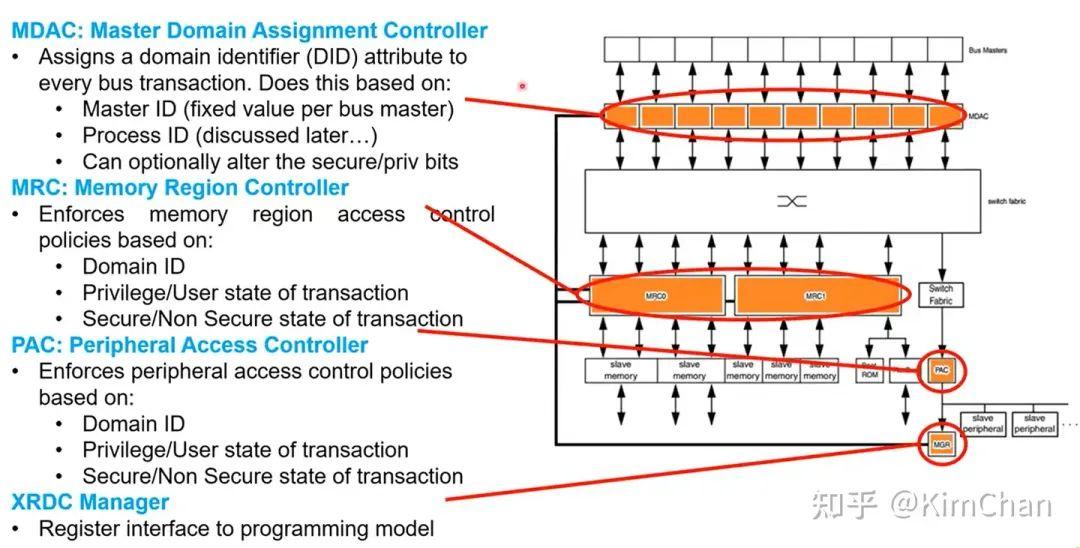

xRDC_MGRпјҡз®ЎзҗҶеӯҗжЁЎеқ—пјҢеҚҸи°ғжүҖжңүзҡ„иҜ»еҶҷж“ҚдҪң

xRDC_MDACпјҡеҹҹеҲҶй…ҚжҺ§еҲ¶еҷЁпјҢеӨ„зҗҶиө„жәҗеҲҶй…Қд»ҘеҸҠеҹҹIDз”ҹжҲҗ

xRDC_MRCпјҡеҶ…еӯҳеҢәеҹҹжҺ§еҲ¶еҷЁпјҢеҹәдәҺйў„зј–зЁӢзҡ„еҢәеҹҹжҸҸиҝ°еҜ„еӯҳеҷЁе®һзҺ°д»ҺеӯҳеӮЁзҡ„и®ҝй—®жҺ§еҲ¶

xRDC_PACпјҡеӨ–и®ҫи®ҝй—®жҺ§еҲ¶еҷЁпјҢеҹәдәҺйў„зј–зЁӢзҡ„еҹҹи®ҝй—®жҺ§еҲ¶еҜ„еӯҳеҷЁе®һзҺ°д»ҺеӨ–и®ҫзҡ„и®ҝй—®жҺ§еҲ¶

S32GжңүдёӨдёӘxRDCе®һдҫӢпјҡxRDC_0пјҲsystem instanceпјүе’ҢxRDC_1пјҲaccelerator subsystem instanceпјүгҖӮ

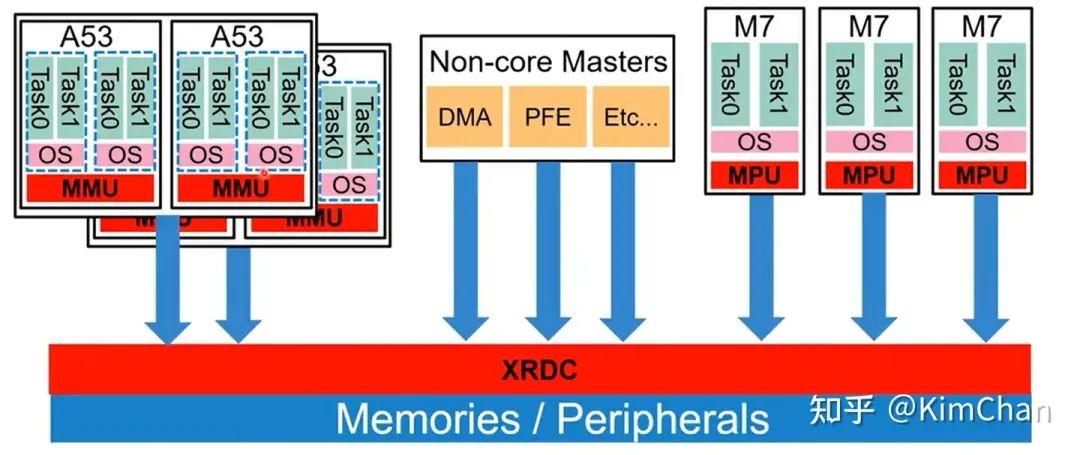

е…ЁеұҖxRDCй…ҚзҪ®е®ҡд№үдәҶ16дёӘеҹҹ(domain)пјҢжҜҸдёӘеҹҹйғҪжңүеӣәе®ҡзҡ„еҹҹеәҸеҸ·гҖӮ

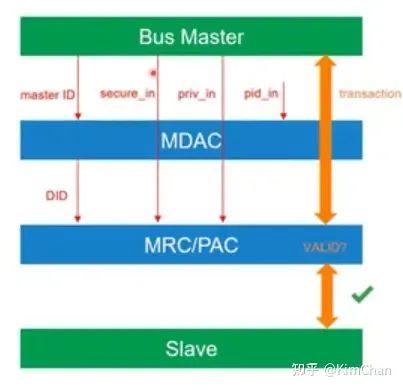

xRDCжҳҜеҰӮдҪ•е·ҘдҪңзҡ„

жҲ‘们д»ҘдёҖдёӘиҜ»ж“ҚдҪңзҡ„жҖ»зәҝдәӢеҠЎдёәдҫӢпјҢBus MasterпјҲMж ёпјүдјҡжҸҗдҫӣд»ҘдёӢдҝЎжҒҜпјҡ

master IDпјҲжҜҸдёӘbus masterйғҪжңүеӣәе®ҡзҡ„еҖјпјҢдҫӢеҰӮCortex-M7_0 AXIжҳҜ8пјү

Secure/non-secure bitпјҲ0д»ЈиЎЁе®үе…Ёи®ҝй—®пјү

Priv/user modeпјҲ1д»ЈиЎЁзү№жқғжЁЎејҸпјү

PIDдјҡе’Ңmaster IDдҝЎжҒҜдёҖиө·иҫ“е…ҘеҲ°MDACпјҢз”ұMDACж №жҚ®иҝҷдёҖеҜ№IDеҲҶй…ҚдёҖдёӘdomain IDгҖӮ

domain IDпјҢsecure_inд»ҘеҸҠpriv_inдҝЎжҒҜдјҡз»ҷеҲ°MRC/PACпјҢеҰӮжһңи®ҝй—®ең°еқҖжҳҜеҶ…еӯҳпјҢеҲҷз”ұMRCеӨ„зҗҶпјҢеҰӮжһңи®ҝй—®ең°еқҖжҳҜеӨ–и®ҫпјҢеҲҷз”ұPACеӨ„зҗҶпјҢMRC/PACеҶіе®ҡжҳҜеҗҰдёәеҗҲжі•и®ҝй—®гҖӮ

йңҖиҰҒжіЁж„Ҹзҡ„жҳҜпјҢxRDCй»ҳи®ӨжҳҜжңӘдҪҝиғҪзҠ¶жҖҒпјҢйңҖиҰҒеңЁеҗҜеҠЁд»Јз Ғдёӯй…ҚзҪ®е№¶дҪҝиғҪгҖӮ

MDAC

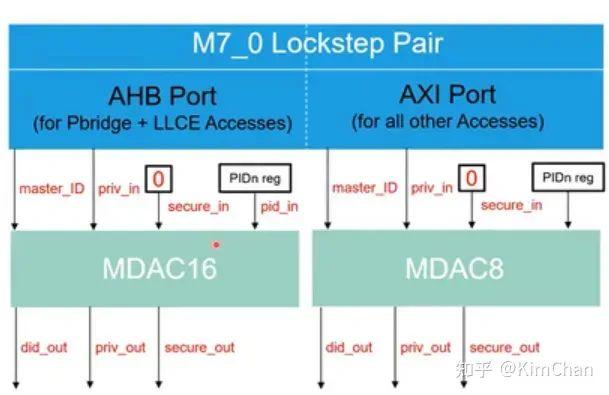

жҜҸдёӘcoreзҡ„AXI/AHBз«ҜеҸЈйғҪжңүеҜ№еә”зҡ„MDACпјҢд№ҹеҚіжҜҸдёӘcoreжңүдёӨдёӘMDACгҖӮ

з”ұдәҺMж ёдёҚж”ҜжҢҒtrust zoneпјҢжүҖд»ҘпјҢйҷӨдәҶзү№ж®Ҡжғ…еҶөеӨ–пјҢжүҖжңүзҡ„и®ҝй—®йғҪиў«и§Ҷдёәе®үе…Ёи®ҝй—®гҖӮ

PrivдҪҚжқҘиҮӘдәҺMж ёжЁЎејҸзҠ¶жҖҒпјҢMDACдёҚж”№еҸҳе®ғгҖӮ

Aж ёжңүtrust zoneпјҢжүҖд»Ҙsecure_inдјҡж №жҚ®е®һйҷ…жғ…еҶөеҸҳеҢ–гҖӮдёҚиҝҮз”ұдәҺAж ёж”ҜжҢҒMMUпјҢе»әи®®дҪҝз”ЁMMUеҜ№еҶ…еӯҳе’ҢеӨ–и®ҫиҝӣиЎҢи®ҝй—®жҺ§еҲ¶гҖӮ

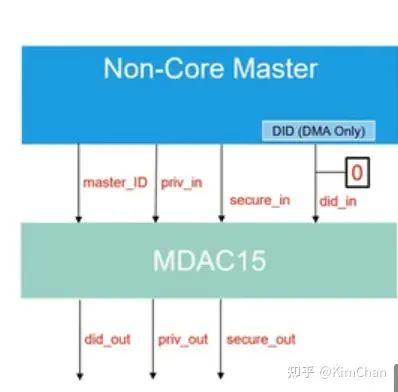

еҜ№дәҺйқһж ёеҝғMasterпјҢдёҚйңҖиҰҒpidиҫ“е…ҘпјҢdid_inдҝЎеҸ·еӣәе®ҡдёә0пјҲeDMCйҷӨеӨ–пјүгҖӮ

MRC/PAC

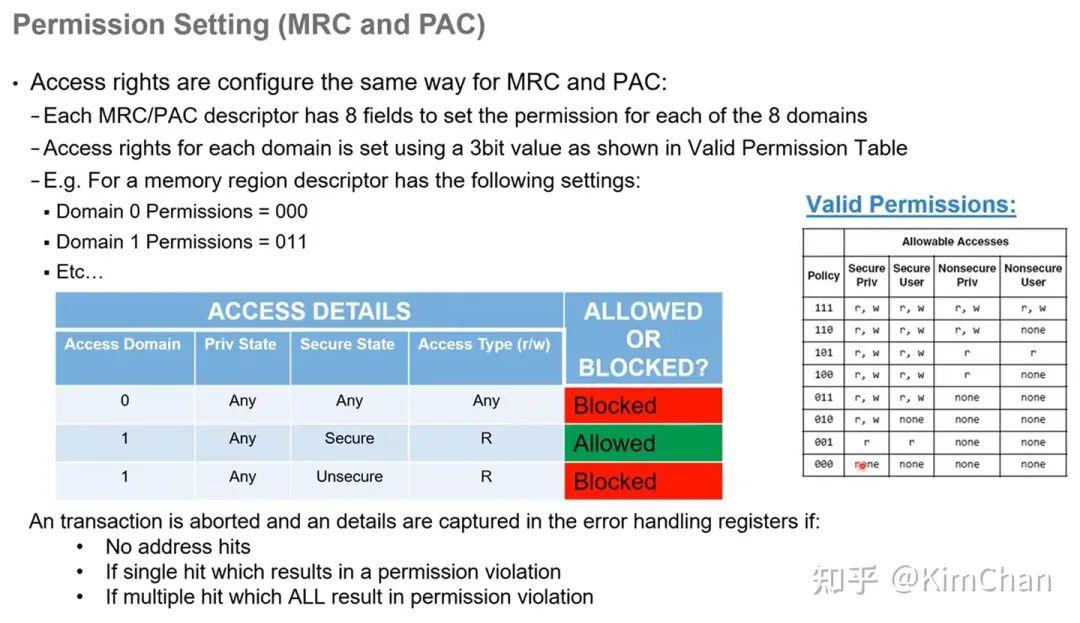

ж №жҚ®slave portжҳҜеӯҳеӮЁиҝҳжҳҜеӨ–и®ҫпјҢеҜ№еә”жңүMRCе’ҢPACгҖӮеҰӮдёҠжүҖиҜҙпјҢе®ғ们еҹәдәҺDomain ID/Priv/SecureдҝЎжҒҜеҶіе®ҡи®ҝй—®жқғйҷҗгҖӮ

еҜ№дәҺMRC/PACй…ҚзҪ®еҜ„еӯҳеҷЁзҡ„и®ҝй—®пјҢеҝ…йЎ»еңЁsecure/privжЁЎејҸдёӢгҖӮ

ж №жҚ®PAC slotеҸ·пјҲйңҖиҰҒеңЁS32Gж–ҮжЎЈйҷ„еёҰзҡ„memory mapдҝЎжҒҜдёӯжҹҘиҜўпјүпјҢPACеҜ№еә”жңүPDAC_Wx_yеҜ„еӯҳеҷЁи®°еҪ•зӣёе…іи®ҫзҪ®пјҢеҰӮжһңDomain ID/Priv/SecureйғҪз¬ҰеҗҲпјҢйӮЈд№ҲеҲҷе…Ғи®ёи®ҝй—®гҖӮ

MRCжөҒзЁӢзұ»дјјпјҢж №жҚ®жүҖеңЁең°еқҖиҢғеӣҙпјҢжҹҘиҜўеҜ№еә”зҡ„MRCxжҺ§еҲ¶еҷЁпјҢеҹәдәҺMRGD_Ww_xеҜ„еӯҳеҷЁи®ҫзҪ®еҲӨж–ӯжҳҜеҗҰжңүжқғйҷҗи®ҝй—®гҖӮ

й”ҷиҜҜеӨ„зҗҶ

еҪ“еҸ‘з”ҹйқһжі•и®ҝй—®ж—¶пјҢй”ҷиҜҜдҝЎжҒҜдјҡи®°еҪ•еңЁеҹҹй”ҷиҜҜеҜ„еӯҳеҷЁдёӯгҖӮ

DERRLOCnпјҡе“ӘдёӘPAC/MRCи§ҰеҸ‘зҡ„й”ҷиҜҜ

DERRm_W0пјҡи®ҝй—®зҡ„ең°еқҖ

DERRm_W1пјҡй”ҷиҜҜеұһжҖ§пјҢдҫӢеҰӮе“ӘдёӘMRCпјҢд»Җд№Ҳзұ»еһӢзҡ„и®ҝй—®пјҢе“ӘдёӘеҹҹ

DERRm_W2пјҡжңӘдҪҝз”Ё

DERRm_W3пјҡејӮеёёе®ҢжҲҗеҗҺеҶҚж¬ЎеҗҜз”Ёд»ҘдёҠеҜ„еӯҳеҷЁпјҢжӯӨж—¶W0/W1дҝЎжҒҜиў«жё…йҷӨ

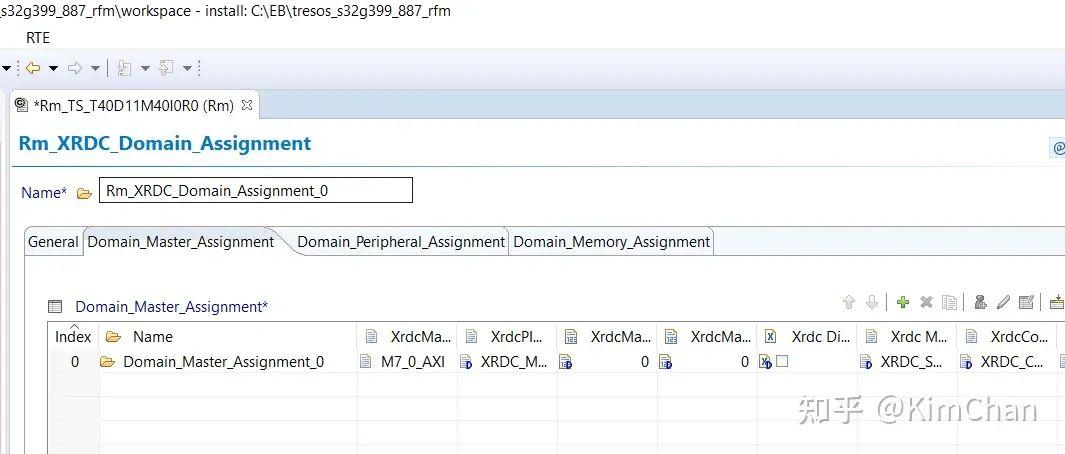

Nxp RmжЁЎеқ—еҸҜд»Ҙй…ҚзҪ®xRDCгҖӮ

еҸӮиҖғ

гҖҗзҺ©иҪ¬еӨҡж ёејӮжһ„гҖ‘еӨ„зҗҶеҷЁеҜ№е…ұдә«еӨ–и®ҫе’Ңиө„жәҗзҡ„и°ғй…Қж–№жі•_еҚЎеҚЎзҪ—зү№GTзҡ„еҚҡе®ў-CSDNеҚҡе®ў

Understanding the S32G Extended Resource Domain Controller (XRDC) | NXP Semiconductors

Extended Resource Domain Controller xRDC