最近有使用到risc-v的单片机,所以了解了下risc-v单片机的编译与调试环境的搭建,面试时问到risc-v的调试可参看以下内容。

risc-v根据官方的推荐,调试器服务是选择OpenOCD,DopenOCD(开放片上调试器)是一个开源的片上调试器,旨在提供针对嵌入式设备的调试、系统编程和边界扫描功能。OpenOCD的功能需要调试仿真器来辅助完成,调试仿真器是一个提供调试目标电信号的小型硬件单元。常用的有JLINK、STLink等一些开发板直接集成了调试仿真器.

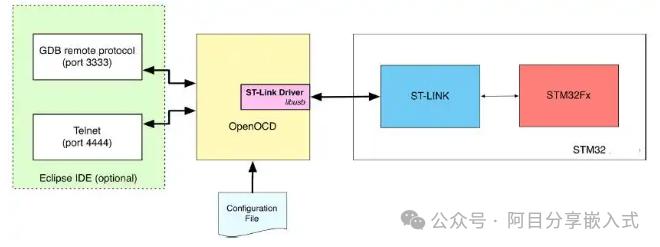

基于openOCD的调试架构如下图所示:

PC端可以是GDB编译调试端或者是一个集成的IDE开发环境,它包含了一个OpenOCD的驱动,这个驱动是根据具体芯片有所差别的,OpenOCD提供了一系列调试的接口,芯片厂生产的芯片要支持OpenOCD就需要做自己家的驱动软件,还有一部分的配置文件(xx.cfg)是用来在上层配置具体芯片型号和调试器硬件类型以及flash编程信息的。cfg文件分几种类型如下:

interface :这些用于调试适配器。指定要使用的配置的文件 特定的JTAG,SWD和其他适配器在这里。

board :关于电路板,PWA,PCB,他们有很多名字。主板文件 包含特定于板的初始化项。

target :关于芯片。“target ”目录代表JTAG TAP。在芯片上 OpenOCD应该控制哪个,而不是一个板子。两种常见的目标类型 是ARM芯片和FPGA或CPLD芯片。当一个芯片有多个TAP(也许它同时具有ARM和DSP内核)时, 目标配置文件定义了所有这些。

可见OpenOCD的github: https://github.com/openocd-org/openocd

对比基于ARM内核的调试架构,可以看到基本结构类似,JLINK定义了一个软件调试层面的RDI接口标准,即Remote debug interface. Keil、IAR、ADS这些开发环境按照RDI标准进行定制,即可以支持JLINK调试。RDI底层使用USB传输,当然,其他硬件接口也是可以的。ARM体系原先是支持JTAG硬件调试接口的,随着cortex系列增加SWD调试规范,现在越来越多的调试器选择SWD接口。其接线少,速率高,也比较稳定。JTAG 20个口太占用pin资源了。JLINK V6开始支持SWD,现在V8支持已经足够好了。

两种内核的调试架构基本换汤不换药,SEGGER和OpenOCD都提供了标准结构给芯片厂,芯片厂基于自家的芯片实现接口,底层都是通过USB驱动实现PC和调试器的通信,都包含下载算法的思路设计flash 编程方法。

下面就先看看,OpenOCD中的cfg文件配置方法吧,以stm32f4为例:

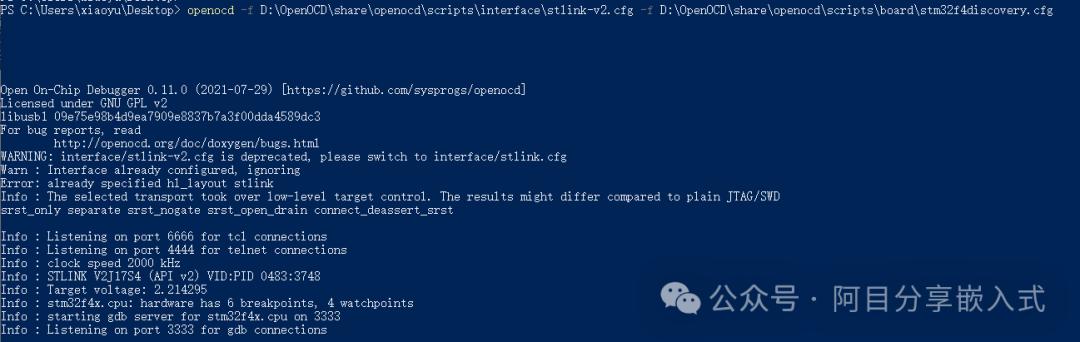

启动openocd服务,需要指定interface和target(target和board可以选择,最小系统板选target, 板载DRAM, 外部Flash的可以带上board的cfg文件)

openocd -f D:\OpenOCD\share\openocd\scripts\interface\stlink-v2.cfg -f D:\OpenOCD\share\openocd\scripts\board\stm32f4discovery.cfg配置内核:

# script for stm32f4x family

## stm32 devices support both JTAG and SWD transports.#source [find target/swj-dp.tcl]source [find mem_helper.tcl]

if { [info exists CHIPNAME] } { set _CHIPNAME $CHIPNAME} else { set _CHIPNAME stm32f4x}

set _ENDIAN little

# Work-area is a space in RAM used for flash programming# By default use 32kB (Available RAM in smallest device STM32F410)if { [info exists WORKAREASIZE] } { set _WORKAREASIZE $WORKAREASIZE} else { set _WORKAREASIZE 0x8000}

#jtag scan chainif { [info exists CPUTAPID] } { set _CPUTAPID $CPUTAPID} else { if { [using_jtag] } { # See STM Document RM0090 # Section 38.6.3 - corresponds to Cortex-M4 r0p1 set _CPUTAPID 0x4ba00477 } { set _CPUTAPID 0x2ba01477 }}

swj_newdap $_CHIPNAME cpu -irlen 4 -ircapture 0x1 -irmask 0xf -expected-id $_CPUTAPIDdap create $_CHIPNAME.dap -chain-position $_CHIPNAME.cpu

tpiu create $_CHIPNAME.tpiu -dap $_CHIPNAME.dap -ap-num 0 -baseaddr 0xE0040000

if {[using_jtag]} { jtag newtap $_CHIPNAME bs -irlen 5}

set _TARGETNAME $_CHIPNAME.cputarget create $_TARGETNAME cortex_m -endian $_ENDIAN -dap $_CHIPNAME.dap

$_TARGETNAME configure -work-area-phys 0x20000000 -work-area-size $_WORKAREASIZE -work-area-backup 0

set _FLASHNAME $_CHIPNAME.flashflash bank $_FLASHNAME stm32f2x 0 0 0 0 $_TARGETNAME

flash bank $_CHIPNAME.otp stm32f2x 0x1fff7800 0 0 0 $_TARGETNAME_WORKAREASIZE 是OpenOcd调试使用的ram空间,一般把flash的编程程序放在这里,然后需要编程的数据也放在这里面。

flash bank $_FLASHNAME stm32f2x 指定flash的名称和驱动,这里如果需要适配自己厂家的芯片的话,flash驱动是需要自己实现的,如果各位小伙伴,以后进入MCU厂,这个flash驱动时必须要会的。关于驱动的写法,阿目有时间再介绍一篇文章,内容比较多。

interface文件中简单配置:

echo "WARNING: interface/stlink-v2.cfg is deprecated, please switch to interface/stlink.cfg"source [find interface/stlink.cfg]只需要配置自己使用是哪个调试硬件平台就好,这是使用的是stlink。

windows powershell 运行界面:

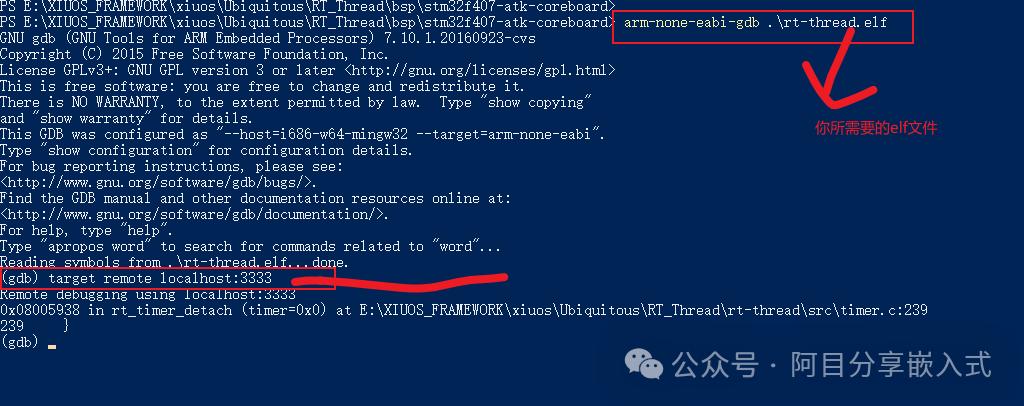

出现上述代表运行正常。其中第一个cfg文件为stlink接口文件 因为用的硬件为stlink,第二个cfg文件为板子对于芯片文件。stm32f407打开另一个cmd或者powershell arm-none-eabi-gdb .\rt-thread.elf

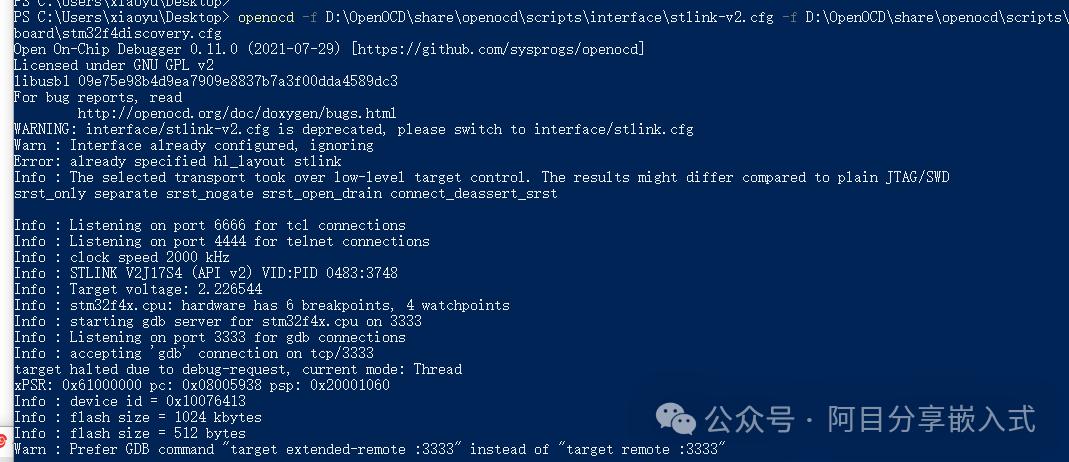

这个时候第一个窗口会显示:

这里的调试截图来源,亲测可用,感谢博主:利用openocd 在windows环境下GDB调试(调试器 stlinkv2)STM32_xpack-openocd 调试stlink-CSDN博客