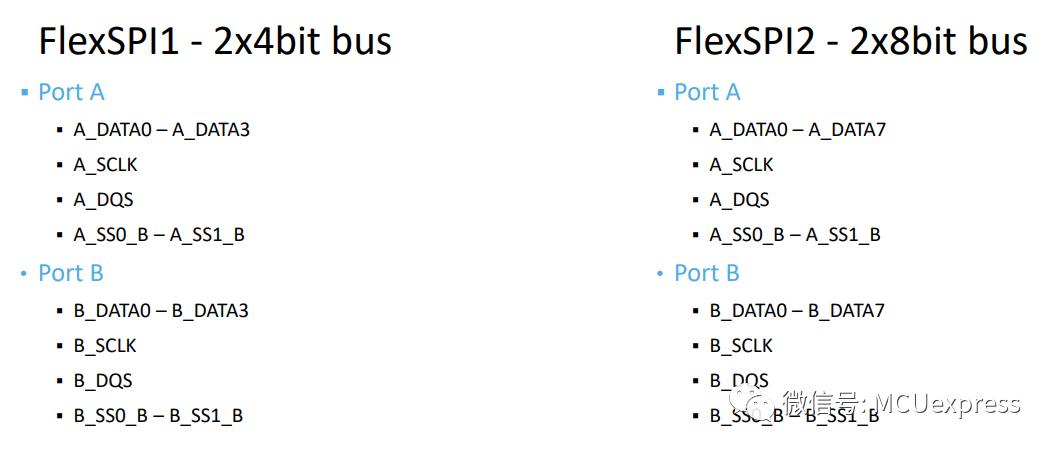

MIMRT1176 MCUжңүдёӨдёӘзҒөжҙ»зҡ„дёІиЎҢеӨ–еӣҙжҺҘеҸЈ-FlexSPI1е’ҢFlexSPI2гҖӮжҜҸдёӘFlexSPIдё»жңәжҺ§еҲ¶еҷЁж”ҜжҢҒдёӨдёӘSPIз«ҜеҸЈ-Aе’ҢBгҖӮжҜҸдёӘз«ҜеҸЈжңҖеӨҡж”ҜжҢҒдёӨдёӘиҠҜзүҮйҖүжӢ©иҫ“еҮәгҖӮFlexSPI2зҡ„жҜҸдёӘз«ҜеҸЈж”ҜжҢҒеҚ•/еҸҢ/еӣӣ/е…«зәҝжЁЎејҸж•°жҚ®дј иҫ“пјҲ1/2/4/8жқЎеҸҢеҗ‘ж•°жҚ®зәҝпјүпјҢиҖҢFlexSPI1зҡ„жҜҸдёӘз«ҜеҸЈйғҪж”ҜжҢҒеҚ•/еҸҢ/еӣӣзәҝжЁЎејҸж•°жҚ®дј йҖҒпјҲ1/2/4жқЎеҸҢеҗ‘ж•°жҚ®зәҝи·ҜпјүгҖӮFlexSPI1дҪҝз”ЁеёҰжңүз«ҜеҸЈAе’ҢBзҡ„4дҪҚжҖ»зәҝпјҢиҖҢFlexSPI2дҪҝз”ЁеёҰжңүз«ҜеҸЈBе’ҢAзҡ„8дҪҚжҖ»зәҝгҖӮ

дё»иҰҒеҠҹиғҪеҢ…жӢ¬пјҡ

вҖўеҗҢж—¶ж”ҜжҢҒSDRжЁЎејҸе’ҢDDRжЁЎејҸ

вҖўж”ҜжҢҒеҚ•зӢ¬/并иЎҢжЁЎејҸ

вҖўHyperBusи®ҫеӨҮпјҲHyperFlash/HHyperRAMпјү

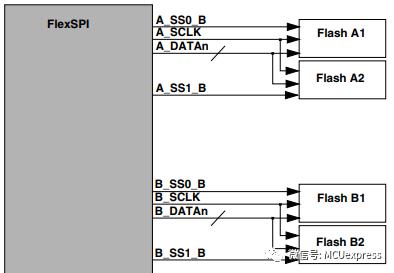

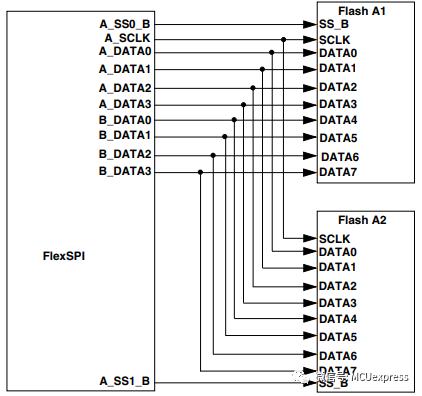

жңүдёӨдёӘ FlexSPIжҺҘеҸЈз«ҜеҸЈпјҲAз«ҜеҸЈе’ҢBз«ҜеҸЈпјүгҖӮжҜҸдёӘз«ҜеҸЈйҖҡиҝҮжҸҗдҫӣ2дёӘиҠҜзүҮйҖүжӢ©иҫ“еҮәжқҘж”ҜжҢҒ2дёӘFlashеҷЁд»¶гҖӮжіЁпјҡFlexSPIй…ҚзҪ®еҸ–еҶідәҺиҠҜзүҮй…ҚзҪ®гҖӮFlexSPIж”ҜжҢҒ 4дёӘеҷЁд»¶зҡ„иҝһжҺҘеӣҫеҰӮдёӢпјҡ

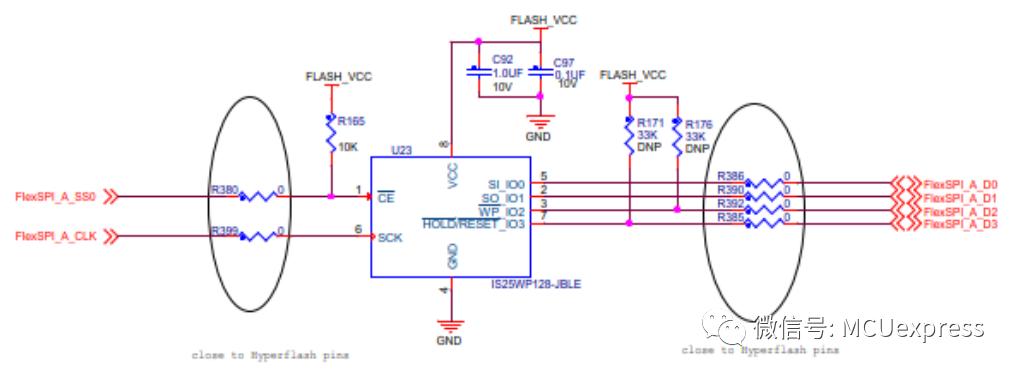

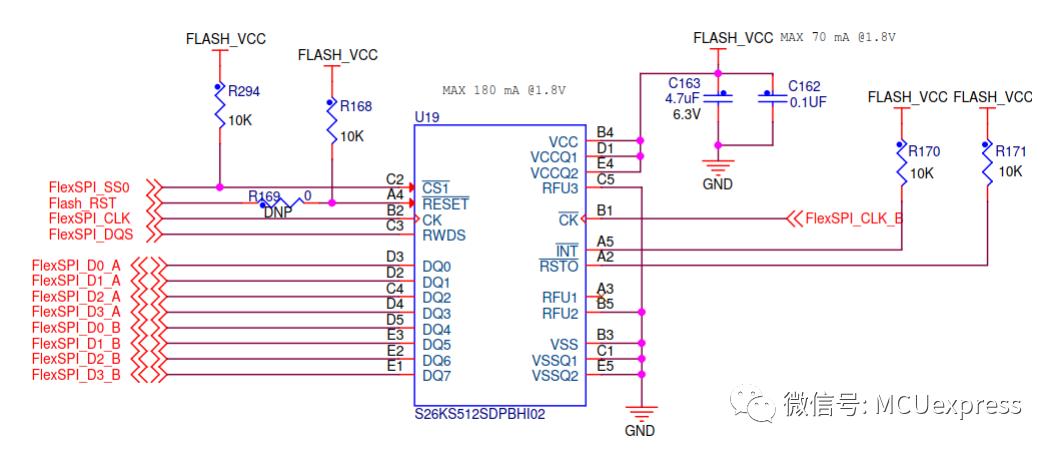

FlexSPI1еҸҜд»ҘеӨ–жҺҘ2зүҮ QSPI FlashеӯҳеӮЁеҷЁпјҢFlexSPI2еҸҜд»ҘеӨ–жҺҘ2зүҮ HyperFlash 8зәҝFlash еӯҳеӮЁеҷЁгҖӮ

вҖўй—ӘеӯҳA1е’ҢA2еҸҜд»ҘжҳҜдёӨдёӘиҠҜзүҮжҲ–еҗҢдёҖеҷЁд»¶е°ҒиЈ…дёҠзҡ„дёӨдёӘй—ӘеӯҳDieгҖӮFlexSPIзҡ„B1е’ҢB2дёҺA1е’ҢA2зӣёеҗҢгҖӮ

вҖўй—ӘеӯҳA1е’ҢB1еҸҜд»ҘдҪҝ用并иЎҢжЁЎејҸ并иЎҢи®ҝй—®гҖӮFlexSPIе°ҶиҮӘеҠЁеҗҲ并/жӢҶеҲҶFlashй—ӘеӯҳиҜ»еҸ–/зј–зЁӢж•°жҚ®гҖӮA2е’ҢB2дёҺA1е’ҢB1зӣёеҗҢгҖӮ

вҖўеңЁе№¶иЎҢжЁЎејҸдёӢпјҢж— жі•еҗҢж—¶и®ҝй—®A1е’ҢA2гҖӮB1е’ҢB2дёҺA1е’ҢA2зӣёеҗҢгҖӮ

вҖўеңЁеҚ•зӢ¬жЁЎејҸдёӢпјҢж— жі•еҗҢж—¶и®ҝй—®A1гҖҒA2гҖҒB1е’ҢB2гҖӮдҪҶиҝҷеӣӣдёӘи®ҫеӨҮеҸҜд»ҘеҚ•зӢ¬и®ҝй—®гҖӮжңүдёҖз§Қз»„еҗҲжЁЎејҸпјҢйҖҡиҝҮе°ҶAз«ҜеҸЈпјҲA_DATA[3:0]пјүе’ҢBз«ҜеҸЈпјҲB_DATA[3:0]]пјүз»„еҗҲеңЁдёҖиө·жқҘжҸҗдҫӣе…«иҝӣеҲ¶ Flash ж”ҜжҢҒгҖӮжӯЈеёёжЁЎејҸд№ҹеҸҜд»Ҙж”ҜжҢҒе…«иҝӣеҲ¶жЁЎејҸпјҢдҪҶAз«ҜеҸЈе’ҢBз«ҜеҸЈ I/Oе®ҪеәҰеә”дёә8гҖӮз»„еҗҲжЁЎејҸиҝһжҺҘеӣҫеҰӮдёӢпјҡ

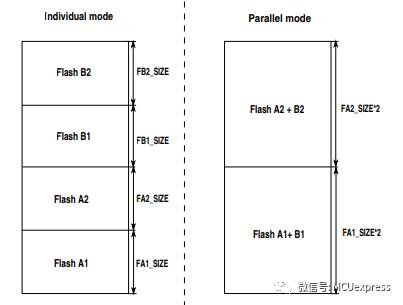

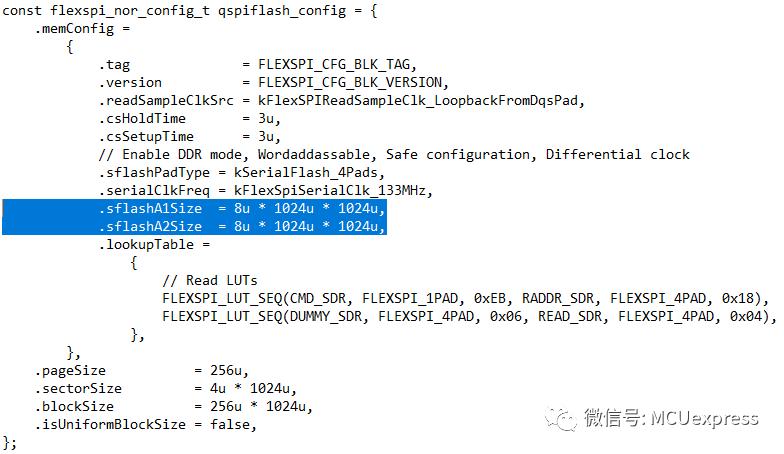

жҜ”еҰӮеңЁFlexspi A1е’ҢA2еҸЈеҗ„жҺҘдёҖдёӘ 8MBзҡ„QSPI FlashпјҢ硬件е…ұз”Ёж—¶й’ҹе’Ңж•°жҚ®зәҝпјҢе°ұеҸӘжҳҜзүҮйҖүдёҚеҗҢгҖӮFlexspi A1дҪңдёәзЁӢеәҸиҝҗиЎҢд»Јз ҒеӯҳеӮЁеҢәпјҢFlexspi A2дҪңдёәж•°жҚ®еӯҳеӮЁеҢәгҖӮA2зҡ„ең°еқҖжҳҜжҺҘзқҖA1зҡ„ең°еқҖи®ҝй—®зҡ„гҖӮеңЁж•°жҚ®и®ҝй—®ж—¶пјҢйңҖиҰҒеҠ дёҠеҒҸ移A1зҡ„ең°еқҖпјҢеҰӮдёӢж“Ұ/еҶҷ/иҜ»ж“ҚдҪңд»Јз ҒзӨәдҫӢдҫӣеҸӮиҖғгҖӮ Flash жҳ е°„еҚ•дёӘе’Ң并иЎҢжЁЎејҸдёӢзҡ„ең°еқҖеҰӮдёӢпјҡ

Flash еӯҳеӮЁеҷЁзӢ¬з«ӢжЁЎејҸдёӢзҡ„ең°еқҖжҳ е°„:

вҖў Flash A1 ең°еқҖиҢғеӣҙ:: 0x00000000 ~ FA1_SIZE

вҖў Flash A2 ең°еқҖиҢғеӣҙ:: FA1_SIZE ~ (FA1_SIZE + FA2_SIZE)

вҖў Flash B1 ең°еқҖиҢғеӣҙ: (FA1_SIZE + FA2_SIZE) ~ (FA1_SIZE + FA2_SIZE + FB1_SIZE)

вҖў Flash B2 ең°еқҖиҢғеӣҙ: FA1_SIZE + FA2_SIZE + FB1_SIZE) ~ (FA1_SIZE + FA2_SIZE + FB1_SIZE + FB2_SIZE)

Flash еӯҳеӮЁеҷЁз»„еҗҲжЁЎејҸдёӢзҡ„ең°еқҖжҳ е°„:

вҖў Flash A1+B1 ең°еқҖиҢғеӣҙ: 0x00000000 ~ FA1_SIZE*2

вҖў Flash A2+B2 ең°еқҖиҢғеӣҙ: FA1_SIZE*2 ~ (FA1_SIZE*2 + FA2_SIZE*2)

FLEXSPI_SetFlashConfig(base, &deviceconfig, kFLEXSPI_PortA1);

FLEXSPI_SetFlashConfig(base, &deviceconfig, kFLEXSPI_PortA2);

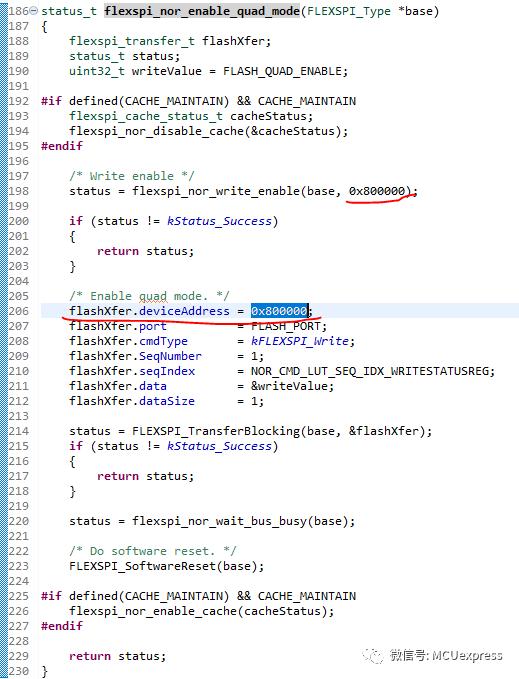

status = flexspi_nor_flash_erase_sector(EXAMPLE_FLEXSPI, 0x800000 + EXAMPLE_SECTOR * SECTOR_SIZE);

status = flexspi_nor_flash_page_program(EXAMPLE_FLEXSPI, 0x800000 + EXAMPLE_SECTOR * SECTOR_SIZE, (void *)s_nor_program_buffer);

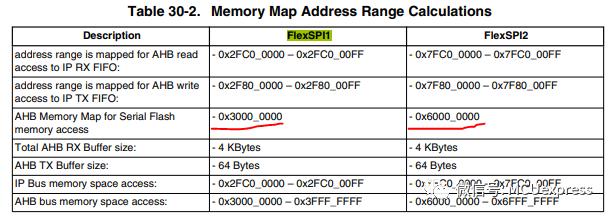

#define FlexSPI1_AMBA_BASE (0x30000000U)

#define EXAMPLE_FLEXSPI_AMBA_BASE FlexSPI1_AMBA_BASE

memcpy(s_nor_read_buffer, (void *)(EXAMPLE_FLEXSPI_AMBA_BASE + 0x800000 + EXAMPLE_SECTOR * SECTOR_SIZE),sizeof(s_nor_read_buffer));

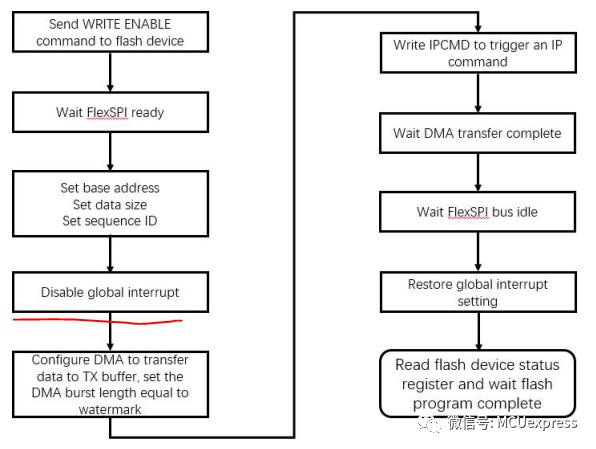

еҪ“е°ҶFlash A1е’ҢFlash A2иҝһжҺҘеҲ°FlexSPIзҡ„з«ҜеҸЈAж—¶пјҢAN12564ж–ҮжЎЈе®һйҷ…дёҠжҸҗдҫӣдәҶдёҖз§Қе®һзҺ°RWWеҠҹиғҪзҡ„ж–№жі•пјҢйҮҮз”Ё DMAдј иҫ“ж–№ејҸгҖӮе»әи®®з”ЁжҲ·е°ҶFlash A1е’ҢFlash B1еҲҶеҲ«иҝһжҺҘеҲ°з«ҜеҸЈAе’Ңз«ҜеҸЈBпјҢд»Ҙе®һзҺ°RWWеҠҹиғҪгҖӮhttps://www.nxp.com/docs/zh/application-note/AN12564.pdf

еңЁAN12564第4йЎөдёӯеҶҷйҒ“пјҢвҖңFlash ж“ҰйҷӨAPIеҠҹиғҪзҡ„йҖҡз”Ёд»Јз Ғд№ҹеҸҜз”ЁдәҺRWWе®һзҺ°пјҢе®ғеңЁSDKеҢ…дёӯеҸҜз”ЁвҖқгҖӮеңЁSDKзҡ„ flexspiпјҲ\driver_examples\flexspiпјүдҫӢзЁӢйЎ№зӣ®дёӯгҖӮ

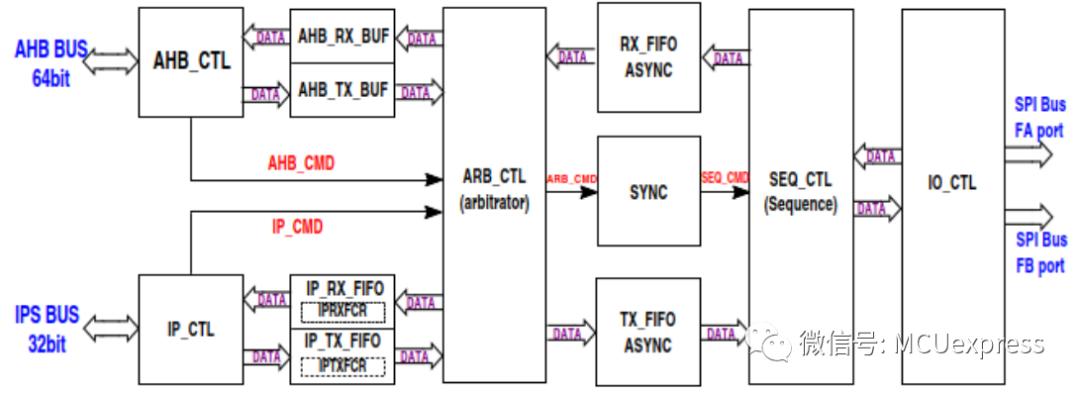

дёәд»Җд№Ҳ CPUдј иҫ“дјҡеҜјиҮҙ硬件 HardFaultпјҹеӣ дёә CPUеҶ…ж ёйҖҡиҝҮ64дҪҚAHBжҖ»зәҝпјҲеҚіAHBе‘Ҫд»Өпјүйў„еҸ–д»Јз ҒпјҢд»Јз ҒзЁӢеәҸйҖҡиҝҮ32дҪҚ IPSжҖ»зәҝпјҲеҚіIP IPе‘Ҫд»Өпјүи°ғз”Ё FlexSPIй©ұеҠЁзЁӢеәҸж“ҰйҷӨжҲ–зј–зЁӢж•°жҚ® FlashгҖӮеҪ“е®ғ们йғҪжғіиҰҒеӨ„зҗҶ Flashж—¶пјҢARB_CTLд»ІиЈҒеҷЁе°ҶзЎ®е®ҡе“Әз§Қзұ»еһӢзҡ„е‘Ҫд»Өе°Ҷдјҳе…ҲжҺ§еҲ¶дёәARBе‘Ҫд»ӨпјҢ并且еңЁйӮЈдёӘж—¶еҖҷеҸӘжңҚеҠЎдәҺдёҖдёӘе‘Ҫд»ӨгҖӮ

еҪ“ DMAе°ҶйЎөйқўж•°жҚ®дј иҫ“еҲ° Flash B1иҝӣиЎҢзј–зЁӢж—¶пјҢжҳҜеҸҜд»Ҙи®© CPUеҒҡе…¶д»–дәӢжғ…пјҲдҫӢеҰӮдёӯж–ӯеӨ„зҗҶгҖҒи®Ўз®—вҖҰпјүпјҢйңҖиҰҒе°Ҷд»Јз ҒйҮҚж–°жҳ е°„еҲ°RAMжүҚиғҪжү§иЎҢгҖӮAN12564第5йЎөеӣҫ5 Flash зЁӢеәҸжөҒзЁӢеӣҫзҰҒз”Ёдёӯж–ӯпјҢзӣҙеҲ°FlexSPIжҖ»зәҝеҶҚж¬Ўз©әй—ІгҖӮ