https://www.nxp.com.cn/docs/en/data-sheet/MC56F80XXX.pdf

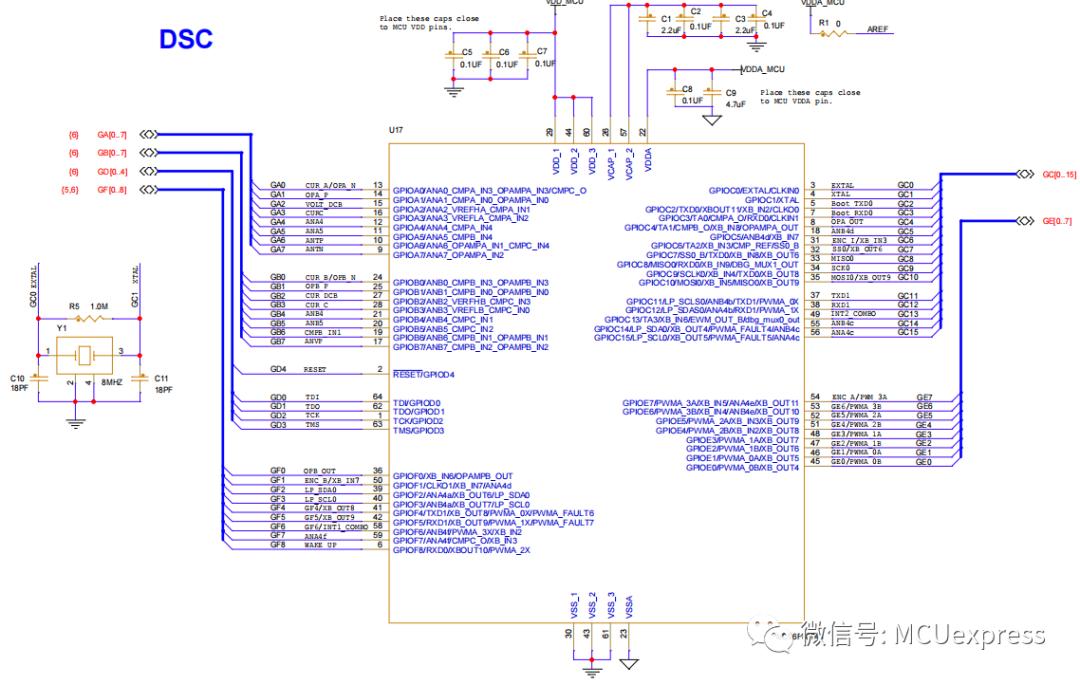

•如果需要,将外部RC电路连接到 RESET引脚。电阻值应在4.7 kΩ–10 kΩ的范围内;电容值应在 0.1µF–4.7µF的范围内。

•在高噪声环境下的正常操作中,将RESET引脚配置为GPIO输出可能有助于提高噪声瞬态抗扰度的性能。

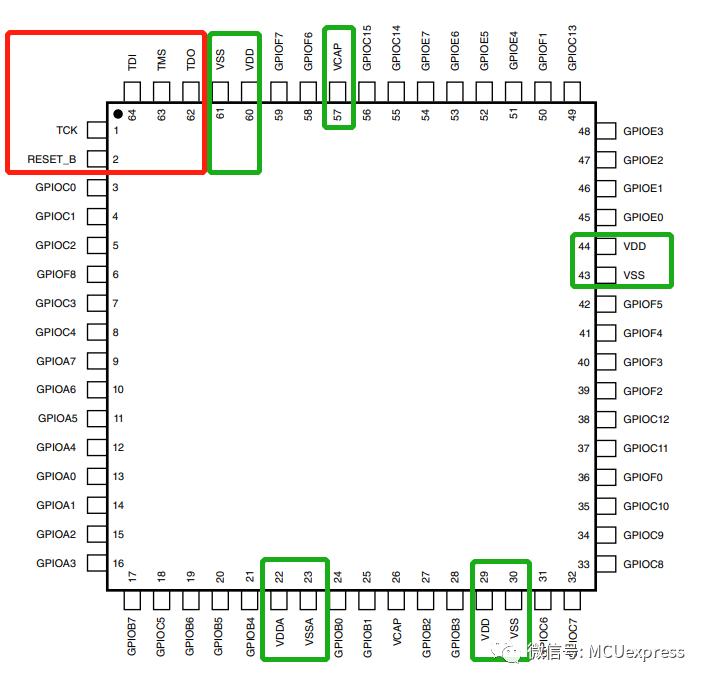

•如果JTAG调试口未连接,在 JTAG端口的TMS引脚上增加2.2 kΩ的外部上拉,以在正常操作期间保持EOnCE处于复位状态。此外,如果操作环境非常嘈杂,则将TMS、TDI、TDO和TCK配置为GPIO。

•在复位期间和复位后,但在I/O初始化之前,所有GPIO引脚都处于三态。

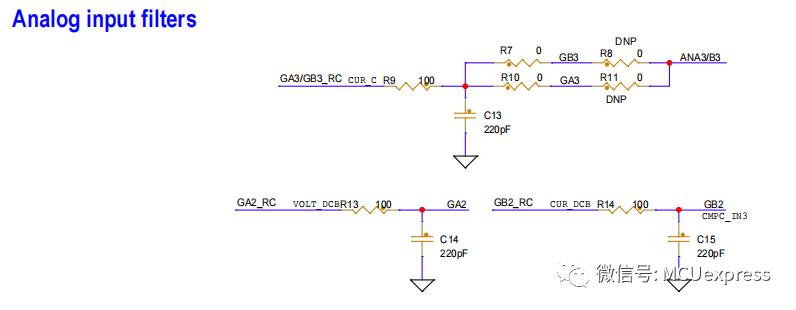

•为消除PCB线阻抗效应,每个ADC输入应具有不小于33pF的10Ω RC滤波。

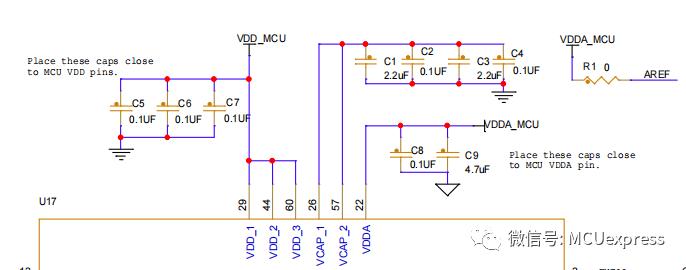

•最低旁路要求是将 0.01–0.1µF电容放置在尽可能靠近电源引脚。推荐的旁路配置在包括VDDA/VSSA的VDD/VSS对中的每一个上放置一个旁路电容。

•确保电容引线和连接到芯片VDD和VSS(GND)引脚,走线尽可能短。

•以大约 10µF加上 0.1µF的退耦合滤波电容数值接在VDD和VSS引脚。

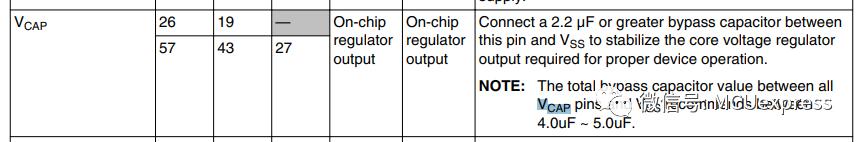

26,57引脚的 VCAP电容推荐是在 4.0-5.0uF之间,以提供稳定的内核电压。

VDD/VSS和VDDA/VSA之间的不适当的上电时序:

建议VDD始终保持在VDDA的100 mV以内,包括电源上升和下降。未能将VDD保持在VDDA的100mV内可能导致漏电流通过VDD和VDDA单元之间的引脚。这种泄漏电流可能会阻止器件通电后的运行。VDD和VDDA之间的电压差必须始终限制在0.3 V以下,以避免对零件造成永久性损坏。

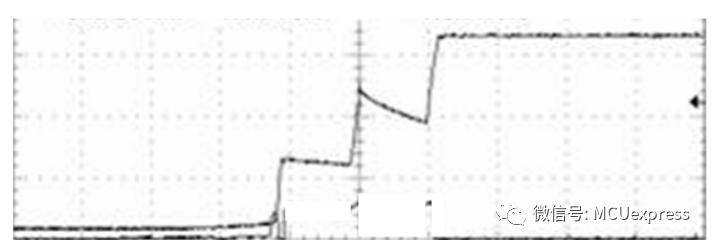

电源输出上的大容性负载:在一些应用中,低成本DC/DC转换器可能无法在输出电压达到大约2.5V到2.7V的调节点之前很好地稳定输出电压。然而,器件可能会在2.3V左右退出复位。如果初始化代码使PLL在复位后立即全速运行DSC,则DSC将从电源中汲取大电流,这可以导致电源电压下降到低于操作电压;请参阅如下图。这可能会导致DSC无法启动。

上电期间建议的初始化顺序为:

POR释放后,从内部振荡器运行几百条NOP指令;这给了电源电压稳定的时间。

将外围设备(ADC除外)配置为所需设置;ADC应当保持在低功耗模式。

接通PLL的电源。

4. PLL锁定后,将时钟从PLL预分频切换到后分频,然后配置ADC。